# Summer Fellowship Report

On

# Integrated Circuit Design using Subcircuit feature of eSim And Device Modelling in eSim

Submitted by

#### Gudivada Jaswanth

B.Tech(Electronics and Communication)

Rajiv Gandhi University of Knowledge Technologies, Srikakulam

Under the guidance of

#### Mr.Sumanto Kar

Assistant Project Manager, FOSSEE, IIT Bombay

### Prof.Kannan M.Moudgalya

Chemical Engineering Department, IIT Bombay

### Acknowledgment

I take this opportunity to express my deepest gratitude to the entire FOSSEE team at IIT Bombay for providing me with this wonderful opportunity to work on the design and integration of sub-circuits using eSim and Device Modelling. The internship has given me valuable exposure to open-source tools, their real-world applications, and a deeper understanding of electronic design and simulation.

I am especially grateful to Prof.Kannan M.Moudgalya for his constant inspiration and vision behind the FOSSEE initiative. His commitment towards promoting open-source software for education and research has created numerous opportunities for students like me to gain hands-on experience and contribute to the open-source community. His farsighted leadership and encouragement have been truly motivating throughout this journey.

I would like to convey my heartfelt thanks to Mr.Sumanto Kar for his constant support, guidance, and encouragement throughout the internship. His valuable insights, timely feedback, and patient mentoring have been instrumental in helping me overcome challenges and successfully complete my project objectives. His dedication towards guiding interns like me has made this journey both enlightening and enjoyable

I also sincerely appreciate the entire FOSSEE initiative for its efforts in empowering students and researchers by making tools freely accessible, thus removing the barriers imposed by costly commercial software. This mission not only fosters innovation but also strengthens the open-source ecosystem, allowing young learners to actively contribute and grow.

This internship has been a memorable and rewarding phase of my academic journey. The knowledge, skills, and experiences I have gained will undoubtedly serve as a strong foundation as I move forward in my career in the semiconductor and VLSI domain.

# Contents

| 1 | Intr | $\mathbf{roduct}$ | ion                                          | 6  |

|---|------|-------------------|----------------------------------------------|----|

|   | 1.1  | eSim              |                                              | 6  |

|   | 1.2  | NgSpi             | ice                                          | 7  |

|   | 1.3  | Make              | rchip                                        | 7  |

|   | 1.4  | KiCao             | d                                            | 8  |

|   | 1.5  | GHDI              | L                                            | 8  |

| 2 | Fea  | tures (           | of eSim                                      | 9  |

| 3 | Pro  | blem              | Statement                                    | 10 |

|   | 1. S | ubcircu           | nit Design and Integration                   | 10 |

|   |      | Appro             | oach                                         | 10 |

|   | 2. D | Pevice 1          | Modeling using Model Editor                  | 12 |

|   |      | Appro             | pach                                         | 12 |

| 4 | Ana  | alog In           | ntegrated Circuit Design                     | 13 |

|   | 4.1  | TLC2              | 201 Adv LinCMOS LOW-NOISE PRECISION OPAMP IC | 13 |

|   |      | 4.1.1             | Key Features                                 | 13 |

|   |      | 4.1.2             | Pin Configuration                            | 14 |

|   |      | 4.1.3             | Op-amp Schematic Diagram                     | 14 |

|   |      | 4.1.4             | Subcircuit test circuit                      | 15 |

|   |      | 4.1.5             | Input Plot                                   | 15 |

|   |      | 4.1.6             | Output Plot                                  | 16 |

|   | 4.2  | TLC2              | 71 LinCMOS PROGRAMMABLE LOW-POWER OPAMP IC   | 17 |

|   |      | 4.2.1             | Key Features                                 | 17 |

|   |      | 4.2.2             | Pin Configuration                            | 17 |

|   |      | 4.2.3             | Op-amp Schematic Diagram                     | 18 |

|   |      | 4.2.4             | Subcircuit test circuit                      | 18 |

|   |      | 4.2.5             | Input Plot                                   | 19 |

|   |      | 4.2.6             | Output Plot                                  | 19 |

|   | 4.3  | TLC2              | 72 LinCMOS PRECISION DUAL OPAMP IC           | 20 |

|   |      | 4.3.1             | Key Features                                 | 20 |

|   |      | 4.3.2             | Pin Configuration                            | 20 |

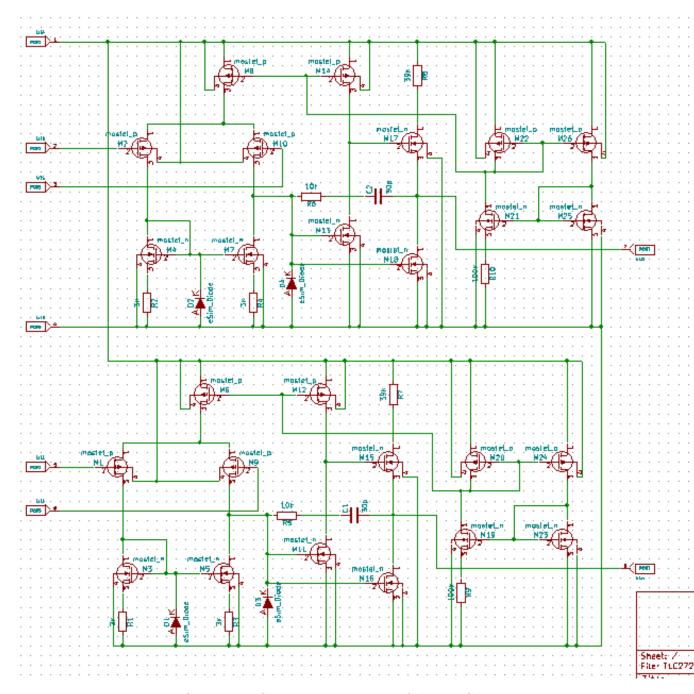

|   |      | 4.3.3             | Op-amp Schematic Diagram                     | 21 |

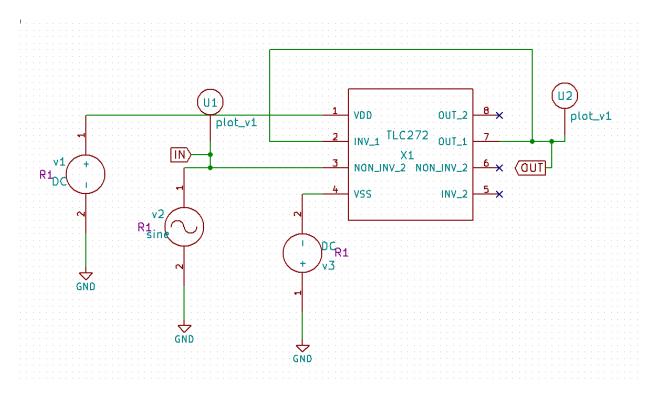

|   |      | 4.3.4             | Subcircuit test circuit                      | 22 |

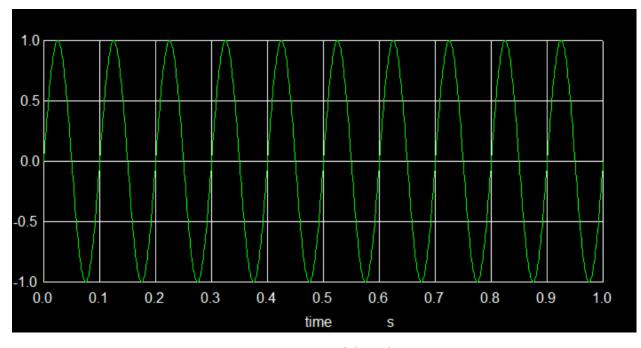

|   |      | 4.3.5             | Input Plot                                   | 22 |

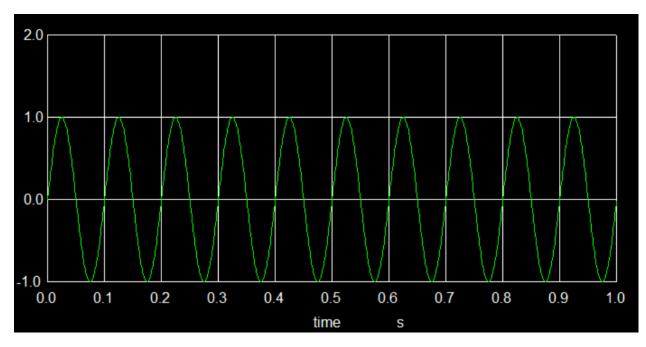

|   |      | 4.3.6             | Output Plot                                  | 23 |

|   | 4.4  | TLC2              | 272 Adv LinCMOS Rail-to-Rail OPAMP IC        | 24 |

|   |      | 4.4.1             | Key Features                                 | 24 |

|      | 4.4.2  | Pin Configuration                                |

|------|--------|--------------------------------------------------|

|      | 4.4.3  | Op-amp Schematic Diagram                         |

|      | 4.4.4  | Subcircuit test circuit                          |

|      | 4.4.5  | Input Plot                                       |

|      | 4.4.6  | Output Plot                                      |

| 4.5  | TLV22  | 21 Adv LinCMOS VERY LOW-POWER SINGLE OPAMP IC 28 |

|      | 4.5.1  | Key Features                                     |

|      | 4.5.2  | Pin Configuration                                |

|      | 4.5.3  | Op-amp Schematic Diagram                         |

|      | 4.5.4  | Subcircuit test circuit                          |

|      | 4.5.5  | Input Plot                                       |

|      | 4.5.6  | Output Plot                                      |

| 4.6  | TLV22  | 11 Adv LinCMOS Rail-to-Rail MICROPOWER OPAMP 31  |

|      | 4.6.1  | Key Features                                     |

|      | 4.6.2  | Pin Configuration                                |

|      | 4.6.3  | Op-amp Schematic Diagram                         |

|      | 4.6.4  | Subcircuit test circuit                          |

|      | 4.6.5  | Input Plot                                       |

|      | 4.6.6  | Output Plot                                      |

| 4.7  | NJU70  | 31 LOW VOLTAGE CMOS OPAMP IC                     |

|      | 4.7.1  | Key Features                                     |

|      | 4.7.2  | Pin Configuration                                |

|      | 4.7.3  | Op-amp Schematic Diagram                         |

|      | 4.7.4  | Subcircuit test circuit                          |

|      | 4.7.5  | Input Plot                                       |

|      | 4.7.6  | Output Plot                                      |

| 4.8  | NJU71  | 08 LOW POWER And LOW OFFSET VOLTAGE CMOS         |

|      | COMF   | PARATOR                                          |

|      | 4.8.1  | Key Features                                     |

|      | 4.8.2  | Pin Configuration                                |

|      | 4.8.3  | Op-amp Schematic Diagram                         |

|      | 4.8.4  | Subcircuit test circuit                          |

|      | 4.8.5  | Input Plot                                       |

|      | 4.8.6  | Output Plot                                      |

| 4.9  | NJU70  | 91A LOW POWER And LOW OFFSET VOLTAGE CMOS        |

|      | OPAM   | IP IC                                            |

|      | 4.9.1  | Key Features                                     |

|      | 4.9.2  | Pin Configuration                                |

|      | 4.9.3  | Op-amp Schematic Diagram 41                      |

|      | 4.9.4  | Subcircuit test circuit                          |

|      | 4.9.5  | Input Plot                                       |

|      | 4.9.6  | Output Plot                                      |

| 4.10 | ICL76  | 660 VOLTAGE CONVERTERS                           |

|      | 4.10.1 | Key Features                                     |

|      | 4.10.2 | Pin Configuration                                |

|      | 4.10.3 | Op-amp Schematic Diagram                         |

|      | 4.10.4 | Subcircuit test circuit                          |

|      | 4.10.5 | Input Plot                                       |

|   |     | 4.10.6 | Output Plot                   | <br> | 45 |

|---|-----|--------|-------------------------------|------|----|

| 5 | DIC | GITAL  | INTEGRATED CIRCUITS DESIGN    |      | 46 |

|   | 5.1 | M8286  | Bidirectional Bus Transceiver | <br> | 46 |

|   |     | 5.1.1  | Key Features                  | <br> | 46 |

|   |     | 5.1.2  | Applications                  | <br> | 46 |

|   |     | 5.1.3  | Pin Configuration             | <br> | 47 |

|   |     | 5.1.4  | IC Schematic Diagram          | <br> | 48 |

|   |     | 5.1.5  | Subcircuit test circuit-1     | <br> | 49 |

|   |     | 5.1.6  | Output Plot-1                 | <br> | 49 |

|   |     | 5.1.7  | Subcircuit test circuit-2     | <br> | 50 |

|   |     | 5.1.8  | Output Plot-2                 | <br> | 50 |

|   |     | 5.1.9  | Subcircuit test circuit-3     | <br> | 51 |

|   |     | 5.1.10 | Output Plot-3                 | <br> | 51 |

|   | 5.2 | M8282  | 2 OCTAL LATCH                 | <br> | 52 |

|   |     | 5.2.1  | Key Features                  | <br> | 52 |

|   |     | 5.2.2  | Applications                  | <br> | 52 |

|   |     | 5.2.3  | Pin Configuration             | <br> | 53 |

|   |     | 5.2.4  | IC Schematic Diagram          | <br> | 54 |

|   |     | 5.2.5  | Subcircuit test circuit       | <br> | 55 |

|   |     | 5.2.6  | Input Plot                    | <br> | 56 |

|   |     | 5.2.7  | Output Plot                   |      |    |

|   | 5.3 | SN545  | 64 4-WIDE AND-OR-INVERT GATES | <br> | 57 |

|   |     | 5.3.1  | Pin Configuration             | <br> | 57 |

|   |     | 5.3.2  | IC Schematic Diagram          | <br> | 58 |

|   |     | 5.3.3  | Subcircuit test circuit       | <br> | 59 |

|   |     | 5.3.4  | Input And Output Plot         | <br> | 59 |

|   | 5.4 | DM74   | 184 BCD-to-Binary Converter   | <br> | 60 |

|   |     | 5.4.1  | Pin Configuration             | <br> | 60 |

|   |     | 5.4.2  | IC Schematic Diagram          |      |    |

|   |     | 5.4.3  | Subcircuit test circuit       | <br> | 62 |

|   |     | 5.4.4  | Input And Output Plot         | <br> | 62 |

|   | 5.5 | DM74   | 185A Binary-to-BCD Converter  | <br> | 63 |

|   |     | 5.5.1  | Pin Configuration             | <br> | 63 |

|   |     | 5.5.2  | IC Schematic Diagram          | <br> | 64 |

|   |     | 5.5.3  | Subcircuit test circuit       | <br> | 65 |

|   |     | 5.5.4  | Input And Output Plot         | <br> | 65 |

| 6 | De  | vice M | Iodeling                      |      | 66 |

|   | 6.1 | 1N914  | HIGH SPEED DIODE              | <br> | 66 |

|   |     | 6.1.1  | Typical Applications          | <br> | 66 |

|   |     | 6.1.2  | SPICE Model Implementation    |      |    |

|   |     | 6.1.3  | Device Model Characterization | <br> | 67 |

|   | 6.2 | 1N581  | 7 SCHOTTKY BARRIER DIODE      |      |    |

|   |     | 6.2.1  | Typical Applications          |      |    |

|   |     | 6.2.2  | SPICE Model Implementation    |      |    |

|   |     | 6.2.3  | Device Model Characterization |      |    |

|   | 6.3 | MV22   | 01 VARACTOR DIODE             |      |    |

|   |     |        | Typical Applications          |      | 74 |

|    |            | SPICE Model Implementation<br>Device Model Characterization |  |  |  |  |  |  |    |

|----|------------|-------------------------------------------------------------|--|--|--|--|--|--|----|

| 7  | Conclusion | and Future Scope                                            |  |  |  |  |  |  | 78 |

| Bi | bliography |                                                             |  |  |  |  |  |  | 79 |

# Chapter 1

## Introduction

The FOSSEE project (Free/Libre and Open Source Software for Education) promotes the use of FLOSS tools to improve the quality of education in our country. The objective is to reduce the dependency on proprietary software in educational institutions. It encourages the use of FLOSS tools through various activities to ensure that commercial software is replaced by equivalent FLOSS tools. It also develops new FLOSS tools and upgrades existing tools to meet requirements in academia and research [1].

The FOSSEE project is part of the National Mission for Education through Information and Communication Technology (ICT), Ministry of Human Resource Development (MHRD), Government of India.

eSim is a free/libre and open source EDA tool for circuit design, simulation, analysis and PCB design developed by FOSSEE, IIT Bombay. It is an integrated tool built using free/libre and open source software such as KiCad, Ngspice, NGHDL and GHDL. eSim is released under GPL.

eSim offers similar capabilities and ease of use as any equivalent proprietary software for schematic creation, simulation and PCB design, without having to pay a huge amount of money to procure licenses. Hence it can be an affordable alternative to educational institutions and SMEs. It can serve as an alternative to commercially available/licensed software tools like OrCAD, Xpedition and HSPICE.

### 1.1 eSim

eSim is an open-source Electronic Design Automation (EDA) tool developed by FOSSEE, IIT Bombay. The primary objective of eSim is to provide a completely free and open-source alternative to commercial circuit design and simulation software, thereby reducing dependency on expensive proprietary tools in academia and research.

eSim integrates multiple open-source tools to provide a comprehensive design and simulation environment. **KiCad** is used for schematic capture and PCB design, while **NgSpice** performs analog circuit simulation. For digital simulation, **GHDL** is integrated, supporting VHDL based designs, and **Makerchip** enables online Trans-

action Level Verilog (TL-Verilog) based digital design and verification. Python support is also available in eSim, allowing users to perform customized simulations, generate netlists.

One of the key features of eSim is its **Subcircuit feature**, which allows complex designs to be modularized into reusable blocks, simplifying the design of large systems. Additionally, eSim supports device modeling, enabling users to define and simulate custom semiconductor devices using real-world parameters. As part of its continuous development, eSim also supports **SkyWater SKY130 PDK**, allowing users to perform simulations using an open-source 130nm Process Design Kit, which is widely used for analog, mixed-signal, and digital IC design research.

By supporting a fully open-source toolchain, eSim empowers students, educators, and researchers to gain hands-on experience with industry-relevant EDA tools and contribute actively to the open-source hardware ecosystem.

### 1.2 NgSpice

NgSpice is an open-source circuit simulator integrated into eSim for performing analog and mixed-signal simulations. Based on the SPICE simulation engine, NgSpice supports DC, AC, transient, and parametric analyses, making it suitable for analyzing a wide range of circuits.

It allows users to simulate circuit behavior using industry-standard SPICE models, including support for subcircuits and behavioral modeling. In eSim, NgSpice works as the backend simulator for schematics created using KiCad, providing waveform outputs for voltage, current, and frequency responses. Its flexibility and accuracy make it a powerful tool for verifying designs before hardware implementation.

### 1.3 Makerchip

Makerchip is an integrated platform designed to simplify digital circuit design by offering both browser-based and desktop-based environments for coding, simulating, and debugging digital hardware designs. It supports multiple hardware description languages including Verilog, SystemVerilog, and Transaction-Level Verilog (TL-Verilog), allowing flexibility for users at various levels of expertise.

In eSim, Makerchip is interfaced through a Python-based application called Makerchip-App, which seamlessly launches the Makerchip IDE for digital design and verification. The platform integrates several open-source and proprietary tools to provide a rich set of features such as real-time simulation, waveform viewing, and code linting, thereby improving design accuracy and productivity.

### 1.4 KiCad

KiCad is an open-source PCB design and schematic capture tool integrated within eSim for creating circuit schematics and generating PCB layouts. It allows users to design multi-layer boards, define custom footprints, and perform design rule checks to ensure design correctness before fabrication.

In eSim, KiCad acts as the primary schematic editor, allowing users to graphically build circuits by placing and interconnecting components from extensive open-source libraries. The designed schematics can directly be used for both simulation and PCB layout generation. KiCad also supports features such as 3D visualization of PCBs, Gerber file export for manufacturing, and electrical rule checking to identify design issues early. Its seamless integration within eSim enables a smooth transition from schematic design to simulation and physical realization, offering a complete design-to-fabrication workflow entirely within an open-source environment.

#### 1.5 GHDL

GHDL is an open-source simulator for VHDL, a hardware description language widely used in digital circuit design. It supports the complete IEEE VHDL standard, allowing designers to simulate, verify, and debug VHDL-based digital systems effectively.

In eSim, GHDL is integrated to enable digital simulation alongside analog simulation provided by NgSpice. Users can model digital circuits using VHDL, which are then simulated using GHDL to verify logical functionality and timing behavior. This integration allows eSim to handle mixed-signal designs, where the analog components are simulated by NgSpice and the digital components by GHDL, providing a comprehensive platform for complex system design. The combination of these tools allows designers to validate both analog and digital subsystems within a unified simulation environment.

# Chapter 2

# Features of eSim

eSim offers a comprehensive set of features that make it a powerful open-source alternative for electronic design automation. Some of the key features include:

- Open-source and Free: eSim is fully open-source, allowing unrestricted access without licensing costs, making it ideal for academic and research purposes.

- Integrated Toolchain: Combines multiple open-source tools such as KiCad for schematic capture and PCB design, NgSpice for analog simulation, GHDL for digital simulation, and Makerchip for advanced digital design.

- Mixed-Signal Simulation: Supports both analog and digital simulation, allowing users to design and simulate mixed-signal circuits efficiently.

- Subcircuit Feature: Enables hierarchical and modular design by allowing complex circuits to be broken into reusable subcircuits.

- **Device Modeling**: Supports custom device modeling, allowing users to simulate real-world semiconductor devices using user-defined parameters.

- SkyWater SKY130 PDK Support: Provides access to open-source 130nm process design kit for IC design and simulation.

- Python Integration: Allows automation, scripting, and advanced analysis using Python interfaces.

- User-Friendly Interface: Offers an intuitive GUI that simplifies circuit creation, simulation setup, and result analysis, making it suitable for both beginners and advanced users.

- Cross-Platform Support: Compatible with major operating systems like Linux and Windows.

- Active Community and Documentation: Extensive documentation, tutorials, and community support provided through FOSSEE ensure smooth learning and troubleshooting.

# Chapter 3

## Problem Statement

To design, develop and test various Analog and Digital Integrated Circuit Models using the sub-circuit feature in eSim and create Device Models using the Model Editor tool. These subcircuits are to be built using the device models already present in the eSim library. After successful testing of these IC models and their integration into the eSim subcircuit library, these models would be useful in the future for circuit designing purposes.

### 1. Subcircuit Design and Integration

As we have access to the datasheets of all the Integrated Circuits(ICs) present in the market, we use these datasheets to get the internal circuit schematics of the individual ICs. Then we use following methodology:

### Approach

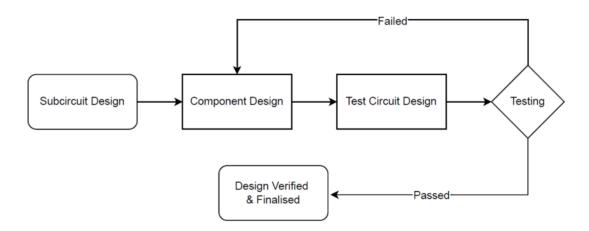

Figure 3.1: Flowchart of IC Design Approach Followed

Our approach to implementing the problem statement involved a systematic process, leveraging datasheets from leading Integrated Circuit (IC) manufacturers such

as Texas Instruments, Analog Devices, and NXP Semiconductors. We focused on selecting ICs with diverse functionalities, including precision amplifiers, comparators.

- Datasheet Analysis: Datasheets from various manufacturers are studied to extract internal circuit diagrams, equivalent schematics, truth tables, pin configurations, and functional blocks.

- Subcircuit Schematics: Draw the internal circuit schematics of the selected ICs in eSim using its subcircuit feature and the device models already present in the eSim devices library. The circuit is designed by strictly following the information given in the datasheet.

- Component Designing: After the subcircuit designing is completed, the component/pin diagram of the respective ICs is drawn according to the data given in the datasheet. Hence, a component is formed with its pin configurations the same as mentioned in the datasheet. This component is saved in the eSim subcircuit library.

- **Test Circuit Design**: These are the circuits that are given in the datasheet as the application of the ICs. Once the component of the IC is drawn and ready to use, we draw their test circuits to test them.

- Simulation and Validation: When the test circuits are completed, various test cases are formed depending on the datasheet information. These ICs are tested against these test cases. If the result comes out to be satisfactory, they are verified else the subcircuit schematic is checked again. Testing is done by using KiCad to Ngspice conversion and then taking out the plots using the simulation feature in eSim.

If the output of the test circuit is not as per expectation, this means that the testcase has failed. In such case we go back to design phase of the IC or the test circuits, to look for possible errors; and then repeat the testing process again after making required changes.

If the expected output of the test cases are correct and satisfies the expected results, then in that case the IC is declared working and verified. The test case has passed successfully and the designing process is complete.

### 2. Device Modeling using Model Editor

To design, develop and test various Analog and Digital Integrated Circuit Models using the sub-circuit feature in eSim and create Device Models using the Model Editor tool. These subcircuits are to be built using the device models already present in the eSim library. After successful testing of these IC models and their integration into the eSim subcircuit library, these models would be useful in the future for circuit designing purposes.

### Approach

- Parameter Extraction: Device parameters like saturation current, ideality factor, capacitances, and breakdown voltage are extracted from datasheets or calculated.

- Model File Creation: The extracted parameters are entered into eSim's Model Editor manually to generate device XML files.

- **Test Circuit Design**: Test circuits are created to validate the newly modeled devices under typical operating conditions.

- Simulation and Validation: The designed test circuits are simulated using NgSpice, and the results are compared with datasheet characteristics to verify accuracy.

# Chapter 4

# Analog Integrated Circuit Design

### 4.1 TLC2201 Adv LinCMOS LOW-NOISE PRE-CISION OPAMP IC

The TLC2201 is a high-precision, low-noise operational amplifier developed using Texas Instruments Advanced LinCMOS<sup>TM</sup> process. It delivers exceptional DC accuracy and low-noise performance, featuring an input offset voltage as low as 80  $\mu$ V and noise levels down to 12  $\mu$ V/Hz at 1 kHz. With rail-to-rail output swing and ultra-low input bias current, it is ideal for high-impedance, low-level signal conditioning. The device supports both single and split-supply configurations, with a common-mode input voltage range that extends to the negative rail. Enhanced by built-in ESD protection (up to 2000 V) and  $\pm 100$  mA latch-up immunity, the TLC2201 is well-suited for robust and precision analog designs.

### 4.1.1 Key Features

- Low noise performance: 30 nV/Hz max at 10 Hz; 12 nV/Hz max at 1 kHz.

- Low input offset voltage: As low as 80 μV (typ.), 200 μV (max for A and B grades).

- Wide operating temperature range:: Up to -55°C to 125°C depending on device suffix.

- **High power supply rejection**: 110 dB, minimizing effects of supply fluctuations.

- Rail-to-rail output swing: Maximizes dynamic range in low-voltage systems.

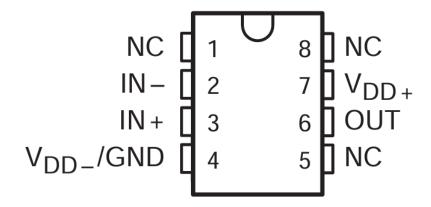

### 4.1.2 Pin Configuration

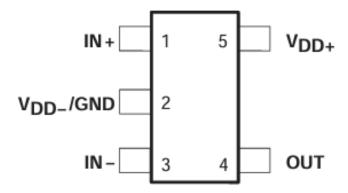

Below is the physical package configuration for the TLC2201, illustrating the pinout arrangement and mechanical layout

Figure 4.1: Pin Configuration of the TLC2201

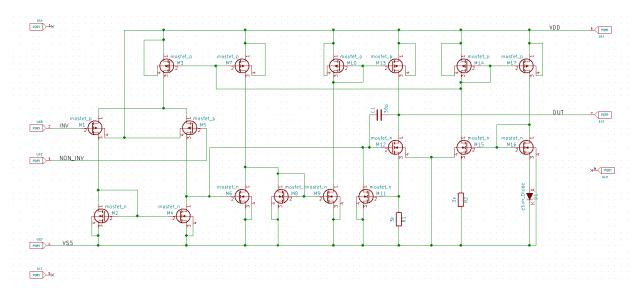

### 4.1.3 Op-amp Schematic Diagram

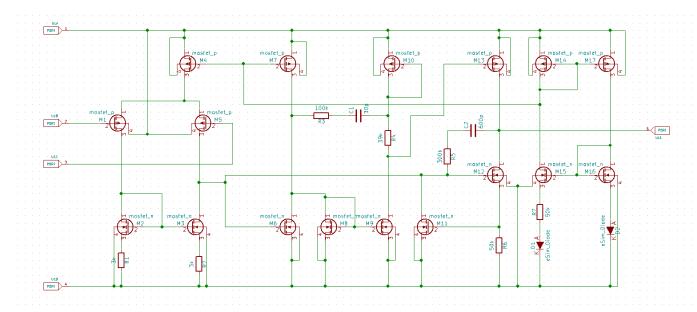

Figure 4.2: Subcircuit Schematic Diagram of the TLC2201

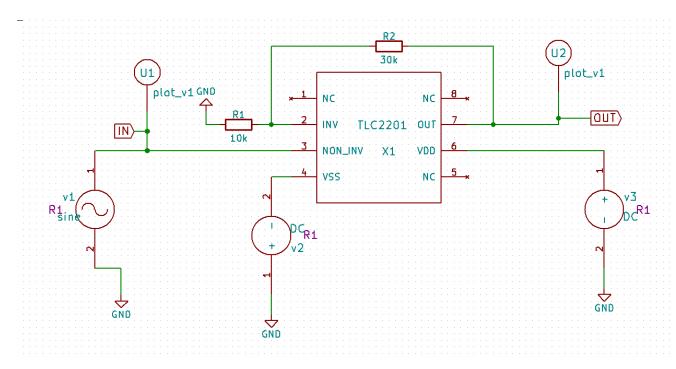

### 4.1.4 Subcircuit test circuit

Figure 4.3: Test Circuit of the TLC2201

## 4.1.5 Input Plot

Figure 4.4: Input Plot of TLC2201

# 4.1.6 Output Plot

Figure 4.5: Output Plot Of TLC2201

### 4.2 TLC271 LinCMOS PROGRAMMABLE LOW-POWER OPAMP IC

The TLC271 is a low-power programmable operational amplifier based on Texas Instruments LinCMOS technology. It features high input impedance, low input offset voltage drift, and operates over a wide supply voltage range from 3 V to 16 V. A key feature is its bias-select capability, allowing selection between low, medium, or high bias modes to balance power consumption and AC performance. It supports single-supply operation and includes ESD protection and latch-up immunity, making it ideal for battery-powered and analog signal applications. The common-mode input range extends below the negative rail, increasing design flexibility.

### 4.2.1 Key Features

- Programmable Performance: AC characteristics like slew rate and gain bandwidth can be tuned via bias mode.

- Bias-Select Functionality: Offers selectable low, medium, and high bias modes to optimize power and performance.

- Rail-to-Rail Input Capability: Common-mode input voltage can go below the negative rail, allowing greater flexibility in single-supply designs.

- Latch-Up Immunity: Designed to resist latch-up, enhancing reliability in harsh conditions.

- ESD Protection: Integrated circuitry protects the TLC271 against electrostatic discharges up to  $\pm 2000$  V, enhancing device reliability and robustness in static-prone environments.

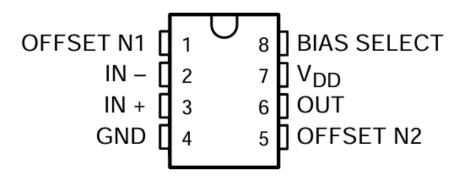

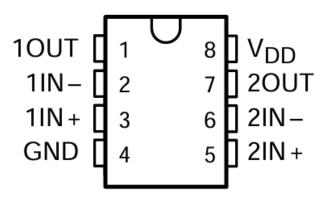

### 4.2.2 Pin Configuration

Below is the physical package configuration for the TLC272, illustrating the pinout arrangement and mechanical layout

Figure 4.6: Pin Configuration of the TLC271

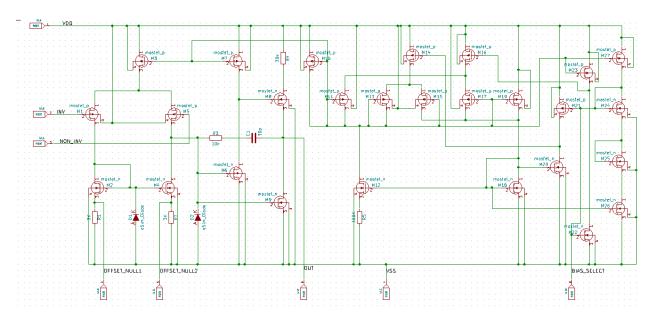

## 4.2.3 Op-amp Schematic Diagram

Figure 4.7: Subcircuit Schematic Diagram of the TLC271

### 4.2.4 Subcircuit test circuit

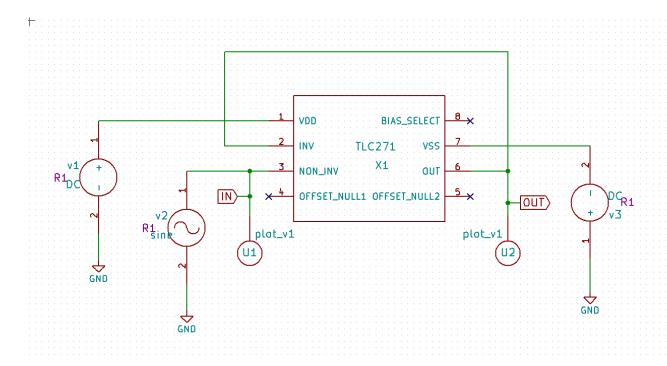

Figure 4.8: Test Circuit of the TLC271

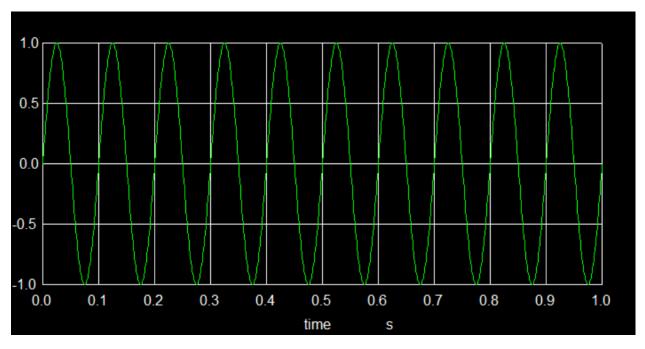

## 4.2.5 Input Plot

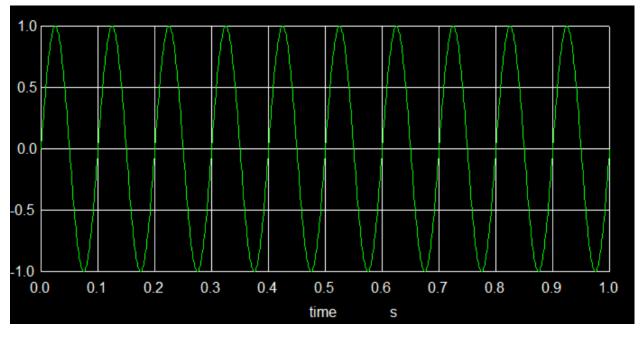

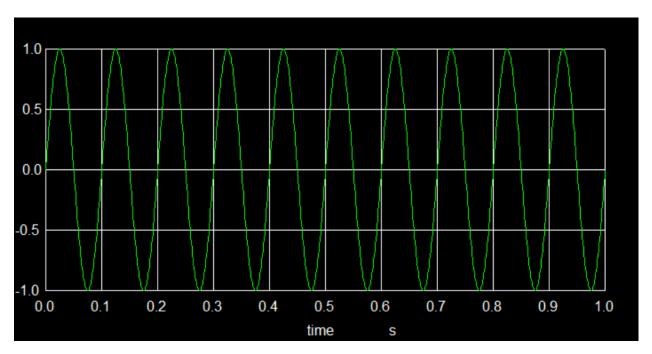

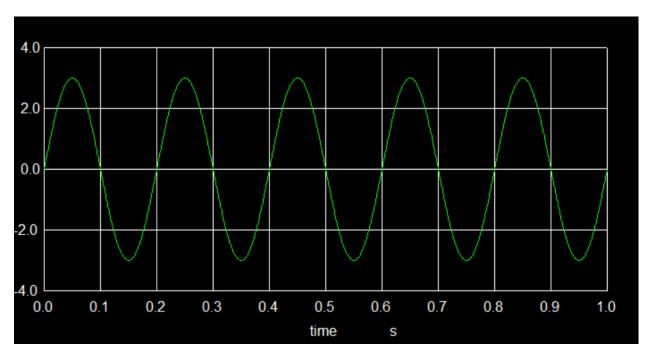

Figure 4.9: Input Plot Of TLC271

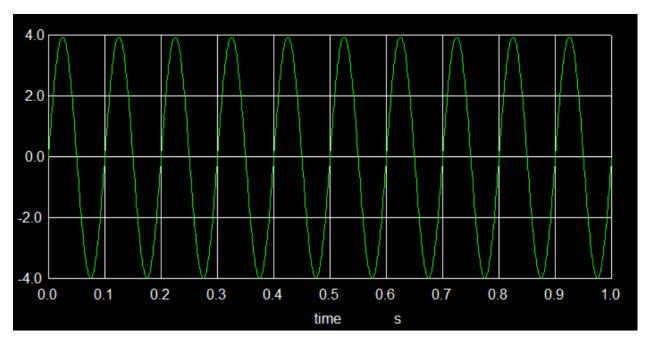

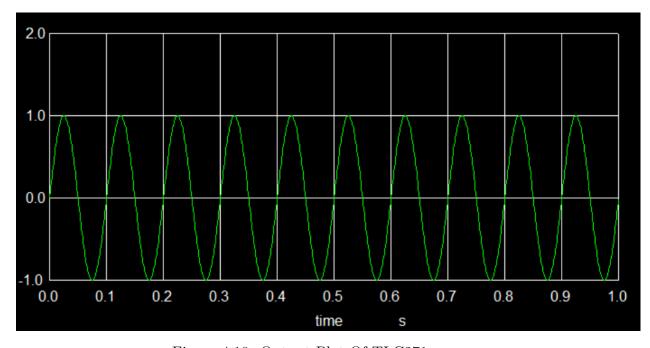

## 4.2.6 Output Plot

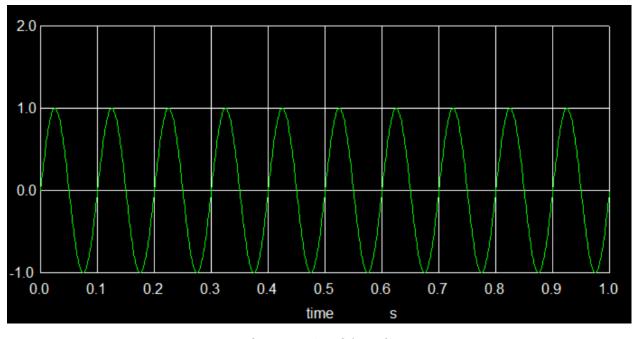

Figure 4.10: Output Plot Of TLC271

# 4.3 TLC272 LinCMOS PRECISION DUAL OPAMP IC

The TLC272 is a dual precision operational amplifier built using Texas Instruments LinCMOS technology, offering high input impedance and low input bias currents. It supports single-supply operation with a wide voltage range from 3 V to 16 V, making it ideal for low-voltage and battery-powered applications. The device features low offset voltage drift and excellent common-mode and power supply rejection ratios. It provides a rail-to-rail input range that includes the negative rail, enhancing flexibility in analog signal designs. With low noise and high slew rate, it suits applications such as active filters, signal conditioning, and transducer interfaces. Additionally, it includes ESD protection and is available in multiple offset grades and compact packages.

### 4.3.1 Key Features

- **Dual Precision Op-Amp**: Contains two independent op-amps with precision performance and low input offset voltage.

- Low Offset Voltage Drift:Offers excellent long-term stability with typical drift around 0.1 μV/month.

- **High Slew Rate**:Offers up to 4.6 V/µs (at 10 V supply), enabling fast signal transitions in dynamic circuits.

- Latch-Up Immunity: Designed to resist latch-up, enhancing reliability in harsh conditions.

- ESD Protection: Integrated circuitry protects the TLC271 against electrostatic discharges up to ±2000 V, enhancing device reliability and robustness in static-prone environments.

### 4.3.2 Pin Configuration

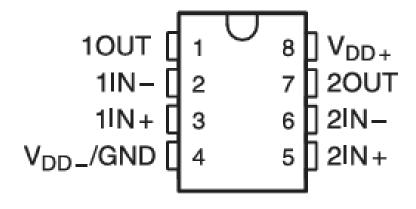

Below is the physical package configuration for the TLC2272, illustrating the pinout arrangement and mechanical layout

Figure 4.11: Pin Configuration of the TLC272

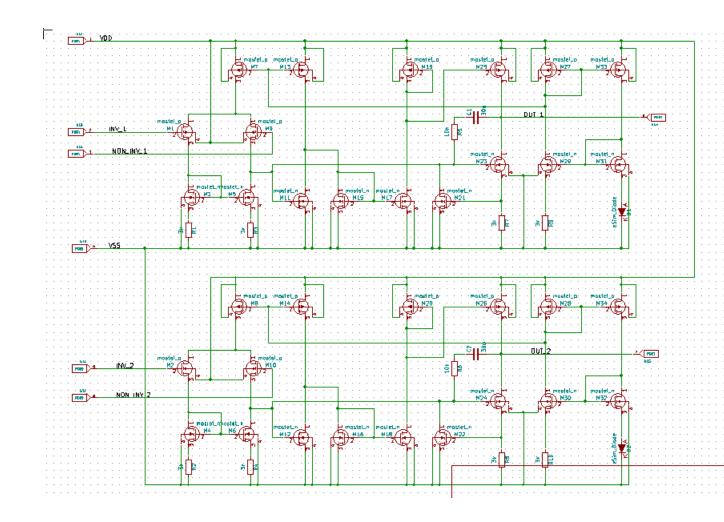

# 4.3.3 Op-amp Schematic Diagram

Figure 4.12: Subcircuit Schematic Diagram of the TLC272  $\,$

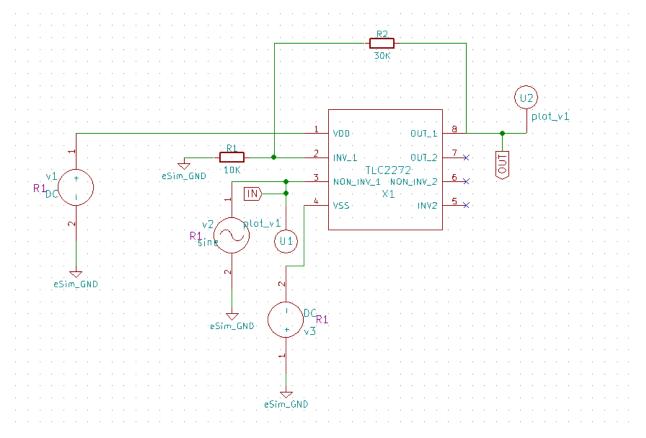

### 4.3.4 Subcircuit test circuit

Figure 4.13: Test Circuit of the TLC272

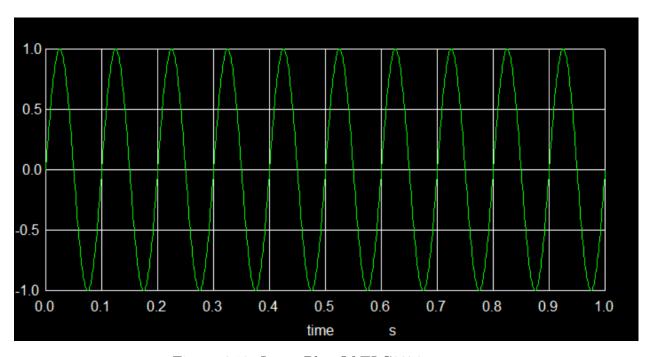

### 4.3.5 Input Plot

Figure 4.14: Input Plot Of TLC272

# 4.3.6 Output Plot

Figure 4.15: Output Plot Of TLC272

# 4.4 TLC2272 Adv LinCMOS Rail-to-Rail OPAMP IC

The TLC2272 is a dual rail-to-rail output operational amplifier developed using Texas Instruments advanced LinCMOS technology. It features a low input bias current (1 pA), low noise (9 nV / Hz at 1 kHz) and operates with single and dual supply configurations ranging from  $\pm 2.2$  V to  $\pm 8$  V. With a high-gain bandwidth product of 2.2 MHz and a slew rate of 3.6 V/micro sec, it is well-suited for higher-speed analog applications. The device offers a low input offset voltage and low power consumption, making it ideal for battery-powered and precision signal conditioning systems. Its rail-to-rail output swing enhances dynamic range, particularly in single-supply systems. Furthermore, TLC2272 is ESD protected and fully characterized in industrial and military temperature ranges

### 4.4.1 Key Features

- High Slew Rate: Provides a typical slew rate of 3.6 V/ $\mu$ s, enabling fast response in signal processing applications.

- Low Input Offset Voltage: Features a maximum input offset voltage of 950 μV (typ. 300 μV), ensuring better accuracy and signal fidelity.

- Low Input Bias Current: Very low input bias and offset currents (typically in the pA range), suitable for high-impedance sensor interfacing.

- Low Power Consumption: Consumes only about 2.2 mA per channel at 5 V, making it efficient for battery-powered applications.

- Rail-to-Rail Output: Supports full output swing to both supply rails, maximizing dynamic range in single- or dual-supply systems.

### 4.4.2 Pin Configuration

Below is the physical package configuration for the TLC2272, illustrating the pinout arrangement and mechanical layout

Figure 4.16: Pin Configuration of the TLC2272

# 4.4.3 Op-amp Schematic Diagram

Figure 4.17: Subcircuit Schematic Diagram of the TLC2272  $\,$

### 4.4.4 Subcircuit test circuit

Figure 4.18: Test Circuit of the TLC2272

### 4.4.5 Input Plot

Figure 4.19: Input Plot Of TLC2272

# 4.4.6 Output Plot

Figure 4.20: Output Plot Of TLC2272

# 4.5 TLV2221 Adv LinCMOS VERY LOW-POWER SINGLE OPAMP IC

The TLV2221 is a low-voltage, single operational amplifier designed using Texas Instruments advanced LinCMOS process. It operates efficiently with a very low supply current (typically 110 µA) and supports supply voltages from 2.7 V to 10 V, making it ideal for battery-powered and portable systems. The amplifier features rail-to-rail output swing and a common-mode input range that includes the negative rail, enhancing its usability in low-voltage applications. With low input bias current (1pA) and low noise, it's well-suited for precision analog and sensor signal conditioning. Its high input impedance and compact SOT-23 package enable space-saving, low-noise PCB layouts. The TLV2221 is fully specified at 3 V and 5 V, ensuring reliable operation in low-power analog designs.

### 4.5.1 Key Features

- Ultra-Low Power Consumption: Operates with a typical supply current of just 110 μA, making it ideal for battery-operated and low-power designs.

- Low Noise Performance: Features low input voltage noise of 19 nV/Hz at 1 kHz, suitable for precision analog signal processing.

- Very Low Input Offset Voltage: With a typical input offset of just 610 μV, it minimizes DC error in analog signal paths.

- Low Harmonic Distortion: Ensures signal fidelity with total harmonic distortion as low as 0.076 % at 1 kHz, ideal for audio and precision circuits.

- Rail-to-Rail Output Swing: The output voltage can swing to both supply rails, maximizing dynamic range in low-voltage applications.

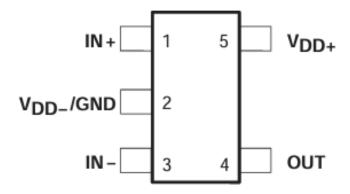

### 4.5.2 Pin Configuration

Below is the physical package configuration for the TLC2221, illustrating the pinout arrangement and mechanical layout.

Figure 4.21: Pin Configuration of the TLC2221

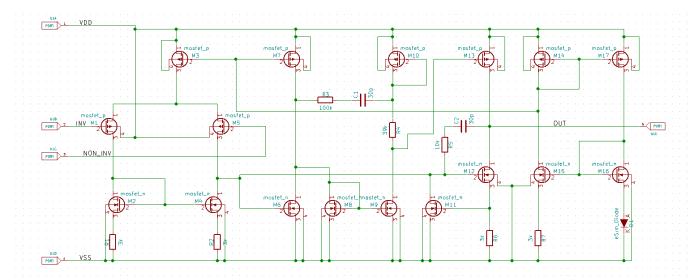

### 4.5.3 Op-amp Schematic Diagram

Figure 4.22: Subcircuit Schematic Diagram of the TLC2221

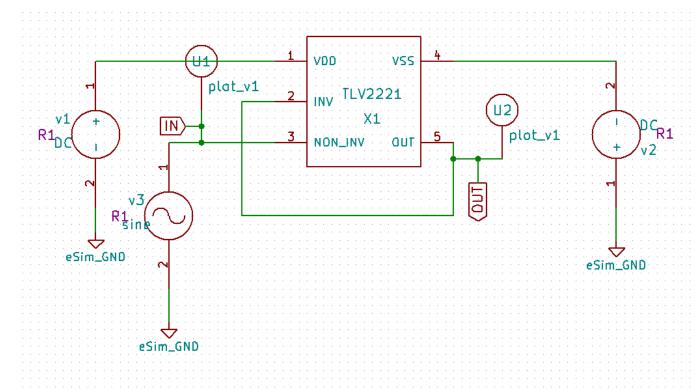

### 4.5.4 Subcircuit test circuit

Figure 4.23: Test Circuit of the TLC2221

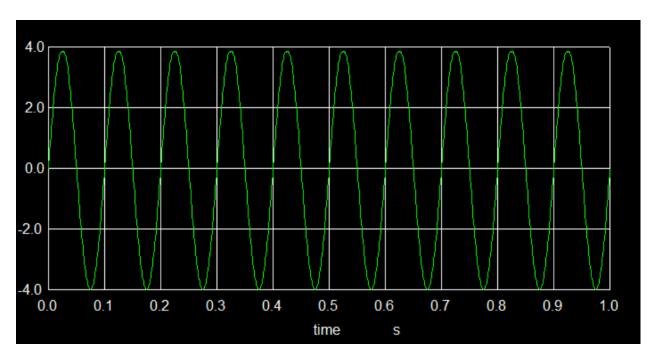

## 4.5.5 Input Plot

Figure 4.24: Input Plot Of TLC2221

## 4.5.6 Output Plot

Figure 4.25: Output Plot Of TLC2221

### 4.6 TLV2211 Adv LinCMOS Rail-to-Rail MICROP-OWER OPAMP

The TLV2211 is a micropower, rail-to-rail output operational amplifier developed using Texas Instruments Advanced LinCMOS process. Designed for single-supply operation from 2.7 V to 10 V, it delivers excellent noise performance and ultra-low power consumption of just 13 µA. It offers high input impedance, extremely low input bias current(1 pA), and a wide common-mode input range that includes the negative rail. With rail-to-rail output swing, it is ideal for low-voltage precision signal conditioning and ADC interfacing. The TLV2211 is fully specified for 3 V and 5 V operation, making it suitable for portable, battery-operated, and sensor-based systems. Its compact SOT-23 packaging and ESD protection further enhance its robustness and integration flexibility.

### 4.6.1 Key Features

- Micropower Operation: Consumes only 13 µA of supply current, making it ideal for energy-critical, battery-powered applications.

- Low Noise Performance: Features low input voltage noise of 21 nV/Hz at 1 kHz, suitable for precision analog signal processing.

- Latch-Up and ESD Protection: Withstands 100 mA surge currents and ±2000 V ESD strikes, enhancing device reliability in harsh environments.

- Ultra-Low Input Bias Current: With a typical input bias current of just 1 pA, it's perfectly suited for high-impedance sensors and precision analog front ends.

- Rail-to-Rail Output Swing: Provides full swing to both supply rails, enhancing dynamic range in low-voltage signal processing systems.

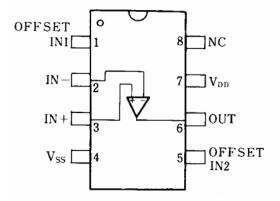

### 4.6.2 Pin Configuration

Below is the physical package configuration for the TLV2211, illustrating the pinout arrangement and mechanical layout .

Figure 4.26: Pin Configuration of the TLV2211

## 4.6.3 Op-amp Schematic Diagram

Figure 4.27: Subcircuit Schematic Diagram of the TLV2211

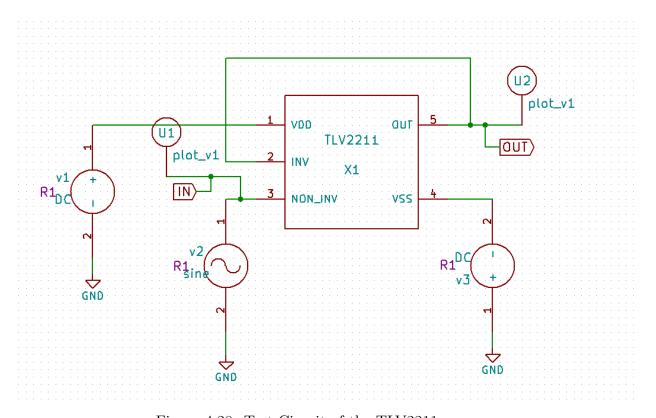

### 4.6.4 Subcircuit test circuit

Figure 4.28: Test Circuit of the TLV2211

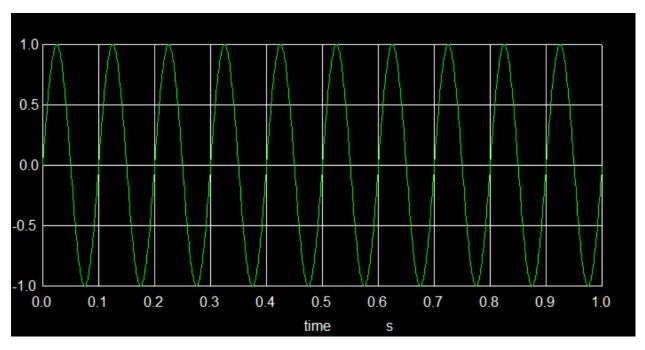

## 4.6.5 Input Plot

Figure 4.29: Input Plot Of TLV2211

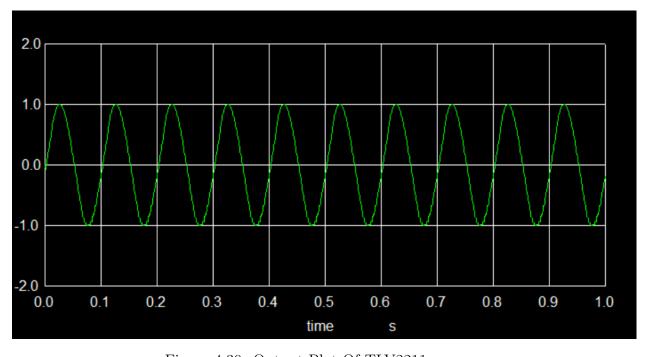

## 4.6.6 Output Plot

Figure 4.30: Output Plot Of TLV2211

# 4.7 NJU7031 LOW VOLTAGE CMOS OPAMP IC

The NJU7031 is a low-voltage, single-supply CMOS operational amplifier designed for precision analog applications. It features a wide operating voltage range from 3 V to 16 V and delivers high slew rate performance of 3.5 V/µs, making it suitable for fast signal processing. The device supports full swing output and a common-mode input range that includes ground, enabling effective operation in single-supply systems. With ultra-low input bias current (1 pA) and low input offset voltage, it is ideal for interfacing with high-impedance sensors. The NJU7031 also includes an external offset null function for improved accuracy. Its compact packaging options support space-efficient, low-power circuit designs

### 4.7.1 Key Features

- **High Slew Rate**: Offers a fast slew rate of 3.5 V/µs, enabling precise and rapid signal transitions in high-speed analog circuits.

- CMOS Technology:Built with advanced CMOS processes, combining low power, high input impedance, and robustness in analog environments.

- Low Power Consumption: Operates at just 1 mA (typ), supporting low-power embedded and portable systems.

- Ultra-Low Input Bias Current: With a typical bias current of 1 pA, it is highly suitable for high-impedance sensor applications like transducers or photodiodes.

- External Offset Null Capability: Allows manual adjustment of offset voltage for enhanced precision—unique to the NJU7031 variant.

### 4.7.2 Pin Configuration

Below is the physical package configuration for the NJU7031, illustrating the pinout arrangement and mechanical layout .

Figure 4.31: Pin Configurations of the NJU7031

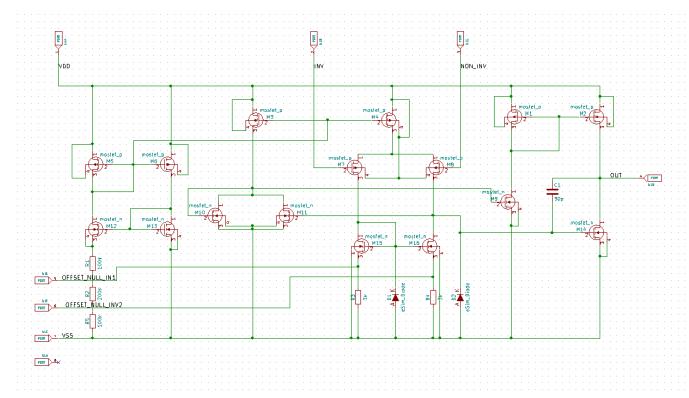

## 4.7.3 Op-amp Schematic Diagram

Figure 4.32: Subcircuit Schematic Diagram of the NJU7031

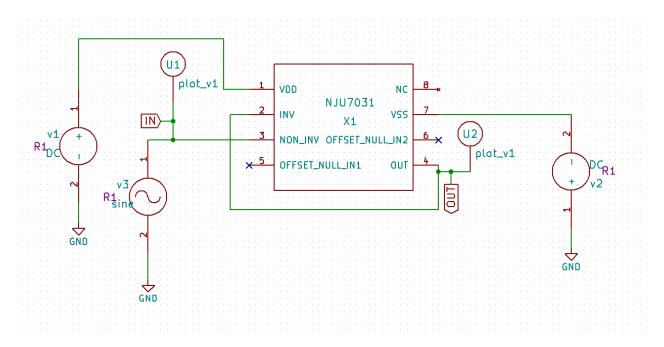

### 4.7.4 Subcircuit test circuit

Figure 4.33: Test Circuit of the NJU7031

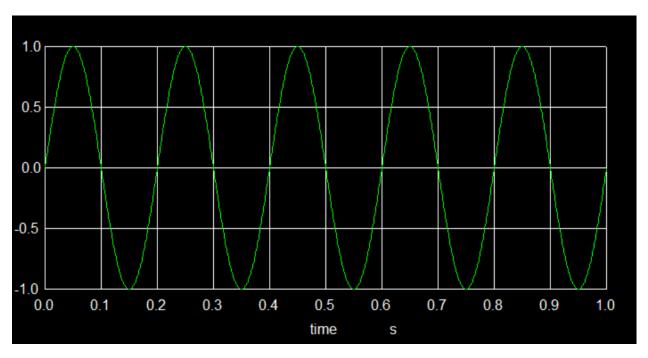

# 4.7.5 Input Plot

Figure 4.34: Input Plot Of NJU7031

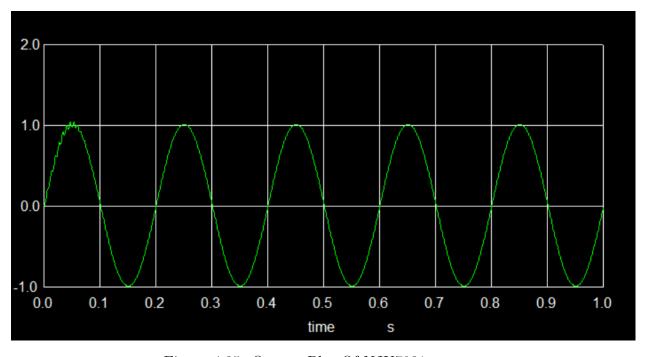

# 4.7.6 Output Plot

Figure 4.35: Output Plot Of NJU7031

# 4.8 NJU7108 LOW POWER And LOW OFFSET VOLTAGE CMOS COMPARATOR

The NJU7108 is a compact, low-power CMOS comparator designed for battery-operated and portable applications. It operates over a wide supply voltage range from 1 V to 5.5 V and features a push-pull output compatible with standard TTL and CMOS logic. With a very low supply current of just 10  $\mu$ A and a maximum input offset voltage of 4 mV, it ensures high efficiency and precision. The comparator supports fast switching, with typical propagation delays under 500 ns. Its ultra-small SC88A and TSON6 packages make it ideal for space-constrained designs. Overall, the NJU7108 is well-suited for low-voltage, high-speed signal detection circuits

#### 4.8.1 Key Features

- Ultra-Low Power Consumption: Operates with just 10 µA typical current, making it highly efficient for battery-operated and portable devices.

- Low Input Offset Voltage:Offers precision with a maximum input offset voltage of only 4 mV, reducing comparator error in sensitive applications.

- Push-Pull Output Stage: Provides strong drive capability with both high and low level outputs, compatible with TTL and CMOS logic systems.

- Compact Package Options: Available in ultra-small SC88A and TSON6 packages, ideal for space-constrained or densely packed PCBs.

- Wide Operating Voltage Range: Functions from 1.0 V to 5.5 V, supporting both low-voltage and standard logic supply levels.

## 4.8.2 Pin Configuration

Below is the physical package configuration for the NJU7108, illustrating the pinout arrangement and mechanical layout  $\cdot$ .

# NJU7108F3 (Top View) NJU7108F3 PIN CONFIGURATION 1. -INPUT 2. V<sub>SS</sub> 3. +INPUT 4. OUTPUT 5. V<sub>DD</sub>

Figure 4.36: Pin configurations of the NJU7108

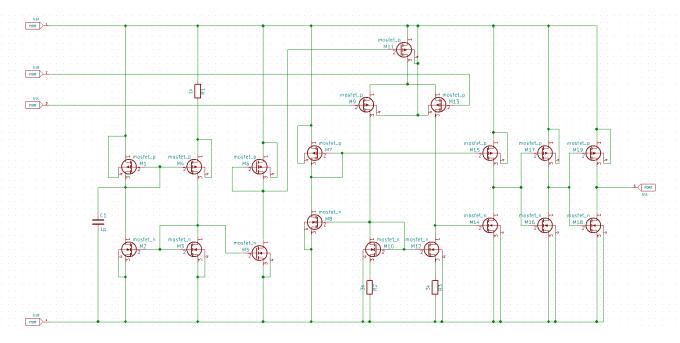

# 4.8.3 Op-amp Schematic Diagram

Figure 4.37: Subcircuit Schematic Diagram of the NJU7108

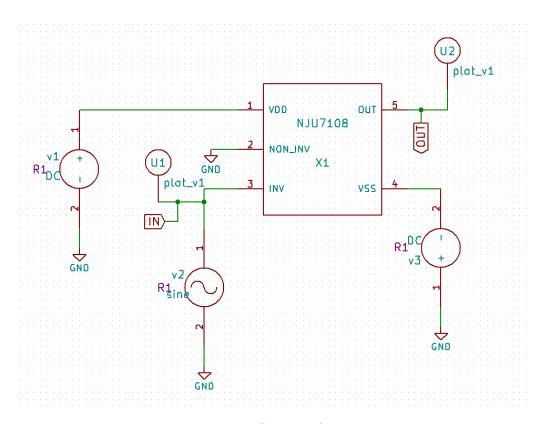

# 4.8.4 Subcircuit test circuit

Figure 4.38: Test Circuit of the NJU7108

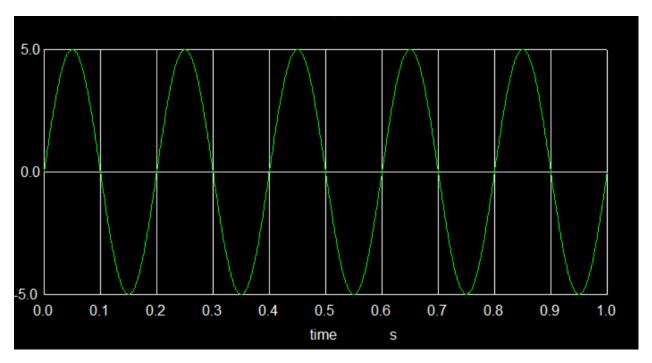

# 4.8.5 Input Plot

Figure 4.39: Input Plot Of NJU7108

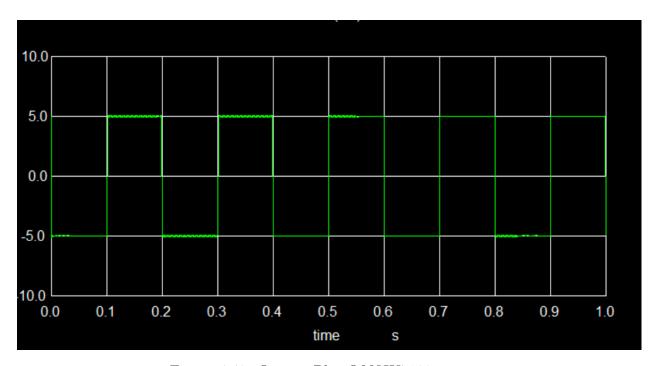

# 4.8.6 Output Plot

Figure 4.40: Output Plot Of NJU7108

# 4.9 NJU7091A LOW POWER And LOW OFF-SET VOLTAGE CMOS OPAMP IC

The NJU7091A is a single low-power CMOS operational amplifier optimized for low-voltage, single-supply applications. Operating over a wide voltage range of 1.8 V to 5.5 V, it consumes minimal current, making it ideal for battery-powered and portable devices. It offers rail-to-rail output swing and excellent input characteristics including low bias current and wide common-mode input range. The device maintains stable operation even at low supply voltages, making it suitable for precision analog signal amplification. With its compact package and low quiescent current, the NJU7091A supports space and power constrained designs. It is especially well suited for sensors, signal conditioning, and portable measurement equipment.

#### 4.9.1 Key Features

- Ultra-Low Power Operation: Consumes very low supply current, ideal for energy-sensitive and battery-powered systems.

- Rail-to-Rail Output Swing: Provides output voltage range that reaches both supply rails, maximizing signal dynamic range.

- Low Input Bias Current: With minimal input current, it's suitable for high-impedance sources such as sensors and transducers.

- Stable at Low Voltages: Ensures reliable performance and consistent output even at lower supply conditions, enhancing circuit robustness.

- Wide Operating Voltage Range: Operates from 1.8 V to 5.5 V, compatible with both low-voltage logic and standard analog systems.

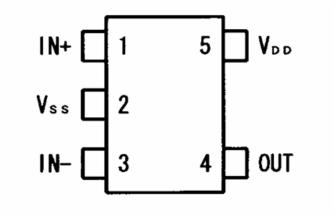

## 4.9.2 Pin Configuration

Below is the physical package configuration for the NJU7091A, illustrating the pinout arrangement and mechanical layout.

Figure 4.41: Pin Configurations of the NJU7091A

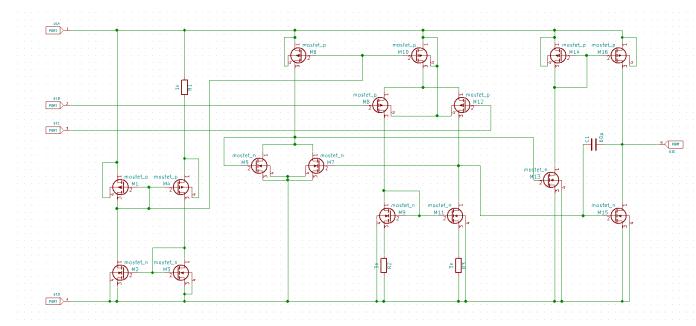

# 4.9.3 Op-amp Schematic Diagram

Figure 4.42: Subcircuit Schematic Diagram of the NJU7091A

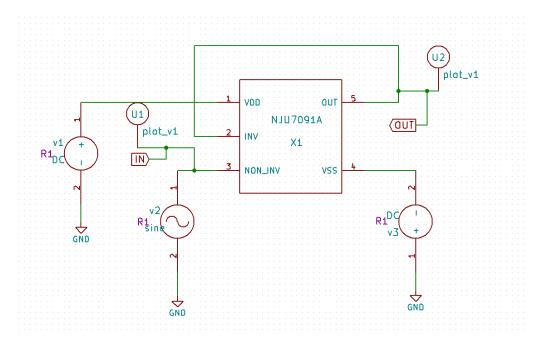

# 4.9.4 Subcircuit test circuit

Figure 4.43: Test Circuit of the NJU7091A  $\,$

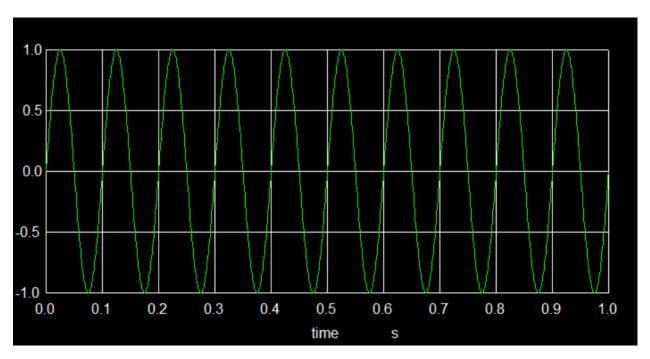

# 4.9.5 Input Plot

Figure 4.44: Input Plot Of NJU7091A

# 4.9.6 Output Plot

Figure 4.45: Output Plot Of NJU7091A

#### 4.10 ICL7660 VOLTAGE CONVERTERS

The ICL7660 is a voltage converter (Vout = -2Vin) designed to generate a negative supply voltage from a positive input, operating within a wide range of +1.5 V to +10 V (or up to +12 V for ICL7660A). It uses a charge-pump technique requiring only two external capacitors, achieving up to 99.9 % voltage conversion efficiency and 98% power efficiency. The device is ideal for creating -5 V from +5 V supplies and can also be configured as a voltage doubler. It features low quiescent current, no need for external diodes, and built-in oscillator and regulation circuitry. With latch-up free operation and simple implementation, it is widely used in portable, analog, and data acquisition systems

#### 4.10.1 Key Features

- **High Conversion Efficiency**: Achieves up to 99.9% voltage conversion efficiency and 98% power efficiency, maximizing performance in power-sensitive designs.

- Simple Implementation: Requires only two inexpensive external capacitors with no external diodes, simplifying PCB layout and reducing BOM cost.

- Negative Voltage Generation: onverts positive input voltages to negative outputs (e.g., +5 V to -5 V), ideal for analog biasing and dual-supply needs.

- Voltage Doubling Capability: Can also be configured as a voltage doubler, generating output voltages up to +18.6 V with a +10 V input.

- Built-in Oscillator and Regulation: Integrates RC oscillator, level translator, and substrate protection for latch-up free, reliable operation.

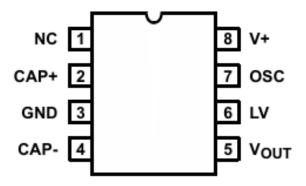

#### 4.10.2 Pin Configuration

Below is the physical package configuration for the ICL7660, illustrating the pinout arrangement and mechanical layout.

Figure 4.46: Pin Configuration of the ICL7660

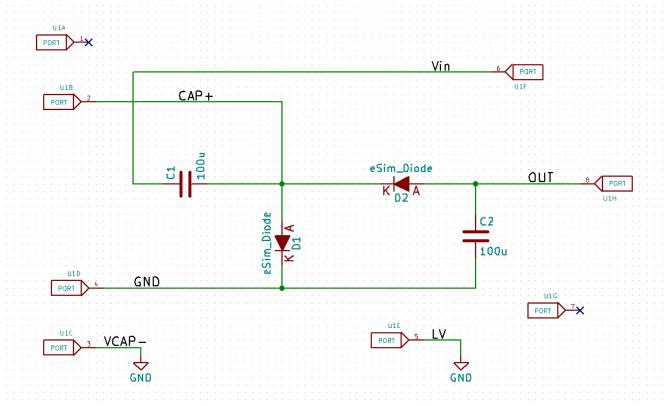

# 4.10.3 Op-amp Schematic Diagram

Figure 4.47: Subcircuit Schematic Diagram of the ICL7660

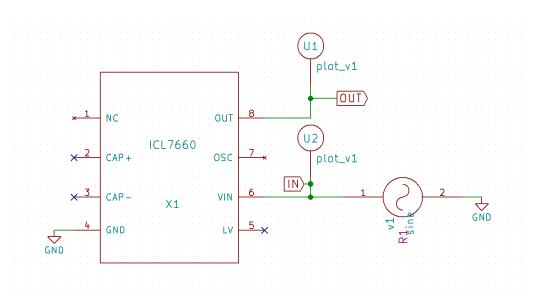

# 4.10.4 Subcircuit test circuit

Figure 4.48: Test Circuit of the ICL7660

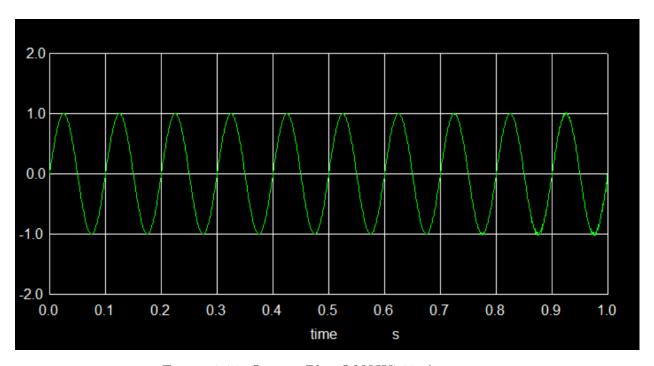

# 4.10.5 Input Plot

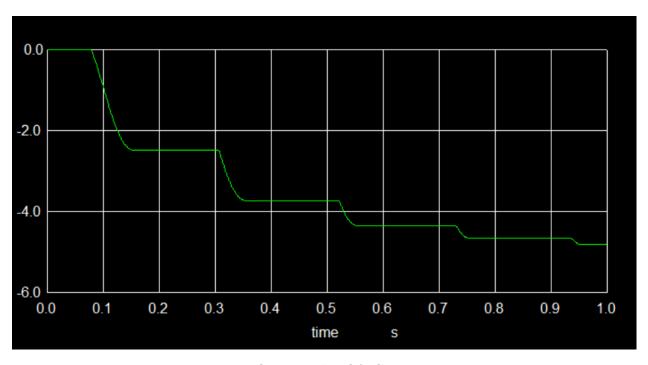

Figure 4.49: Input Plot Of ICL7660

# 4.10.6 Output Plot

Figure 4.50: Output Plot Of ICL7660

Actual Vout = 6V but diodes are not ideal in this circuit so Vout = 6V-1.4V = 4.6V

# Chapter 5

# DIGITAL INTEGRATED CIRCUITS DESIGN

#### 5.1 M8286 Bidirectional Bus Transceiver

The M8286 is a bidirectional bus transceiver designed by Intel, primarily used for data transfer between two buses in microprocessor systems. It supports 3-state outputs and operates in both transmit and receive modes, controlled by active-low enable signals. The device is commonly paired with Intel's 8086/8088 CPUs for buffering address/data lines. It ensures signal integrity during bidirectional communication, especially in multiplexed bus architectures. The M8286 offers high-speed operation and is available in standard 20-pin DIP packages, making it suitable for various system-level applications.

#### 5.1.1 Key Features

- Bidirectional Data Transfer: Supports controlled data flow between two buses, enabling both transmit and receive modes using direction and enable signals.

- Multiplexed Bus Support: Ideal for systems using time-multiplexed address/data buses, such as microprocessor-based architectures.

- **High-Speed Operation**: Designed for rapid data transmission compatible with Intel 8086/8088 microprocessors and similar high-performance systems.

## 5.1.2 Applications

- Microprocessor Systems: Used to interface and buffer the bidirectional address/data bus in systems based on Intel 8086/8088 processors.

- Memory and I/O Interfacing: Facilitates bidirectional communication between CPU and memory or peripheral devices.

- Multi-Master Systems: Allows controlled data exchange between processors or I/O devices in systems with multiple bus masters.

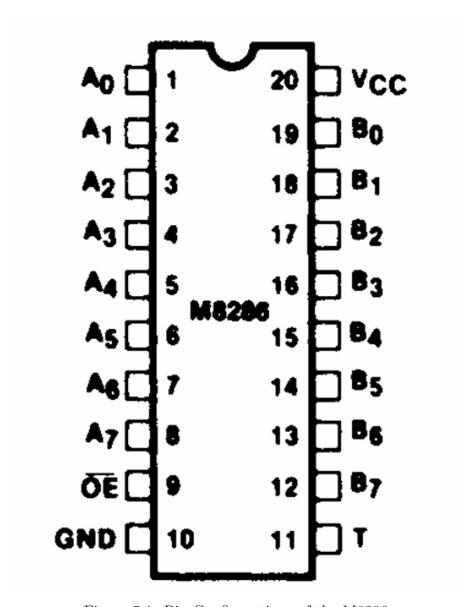

# 5.1.3 Pin Configuration

Below is the physical package configuration for the M8286, illustrating the pinout arrangement and mechanical layout .

Figure 5.1: Pin Configurations of the M8286

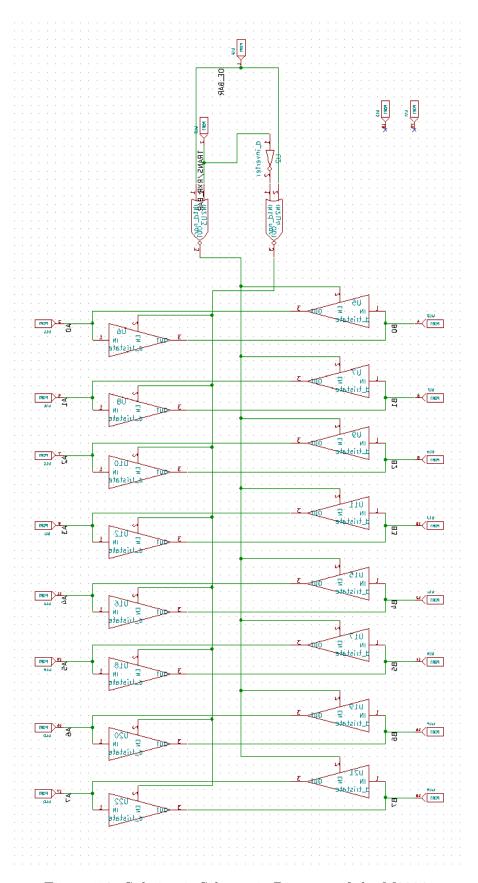

# 5.1.4 IC Schematic Diagram

Figure 5.2: Subcircuit Schematic Diagram of the M8286

# 5.1.5 Subcircuit test circuit-1

Figure 5.3: Data is transferred from A to B when the Trans/RxR pin is set high(Transfering)

Figure 5.4: Trans/Rxr pin is high then Output will be in Volts

# 5.1.6 Output Plot-1

Figure 5.5: Output Plot of M8286

#### 5.1.7 Subcircuit test circuit-2

Figure 5.6: Data is not transfering from A to B when the Trans/RxR pin is set  $Low(Not\ Transfering)$

Figure 5.7: Trans/Rxr pin is Low then output will be in mvolts

# 5.1.8 Output Plot-2

Figure 5.8: Output Plot of M8286

# 5.1.9 Subcircuit test circuit-3

Figure 5.9: Data is transfering from B to A when the Trans/RxR pin is set LOW(Receiving)

# 5.1.10 Output Plot-3

Figure 5.10: Output Plot of M8286

#### 5.2 M8282 OCTAL LATCH

The M8282 is an 8-bit latch designed by Intel for interfacing microprocessors with peripheral devices in memory-mapped I/O systems. It temporarily holds data from the system bus, enabling synchronized communication between the CPU and external hardware. The device features transparent latching and three-state outputs for flexible bus control. It is commonly used to latch address or control signals in Intel 8086/8088-based systems. With fast switching and TTL-compatible inputs/outputs, the M8282 ensures reliable data handling in complex digital systems.

#### 5.2.1 Key Features

- 8-Bit Transparent Latch: Temporarily holds 8-bit data for synchronization between microprocessor and peripheral devices.

- Memory-Mapped I/O: Ideal for use in address or control signal latching in memory-mapped I/O environments.

- **High-Speed Operation**: Designed for fast data transfer in timing-critical applications, compatible with Intel 8086/8088 systems.

- Parallel Data Loading: All 8 bits can be latched simultaneously, simplifying control logic for wide data buses.

## 5.2.2 Applications

- Address Latching in Microprocessor Systems: Used to latch the lower-order address bits (A0–A7) in systems like Intel 8086/8088, enabling address demultiplexing.

- Memory and I/O Interfacing: Facilitates stable communication between the CPU and I/O devices by holding control or data signals.

- Bus Timing Synchronization: Helps align signal timing between fast CPUs and slower peripherals, ensuring reliable data transfer.

- Buffered Data Output: Acts as a temporary data buffer to isolate and control data flow to external components.

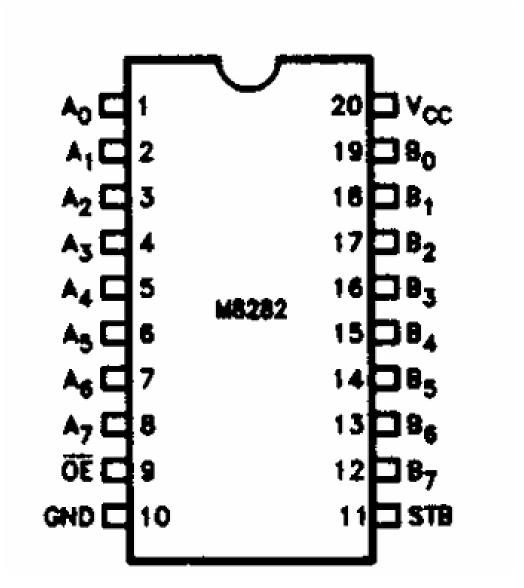

# 5.2.3 Pin Configuration

Below is the physical package configuration for the M8282, illustrating the pinout arrangement and mechanical layout .

Figure 5.11: Pin Configurations of the M8282

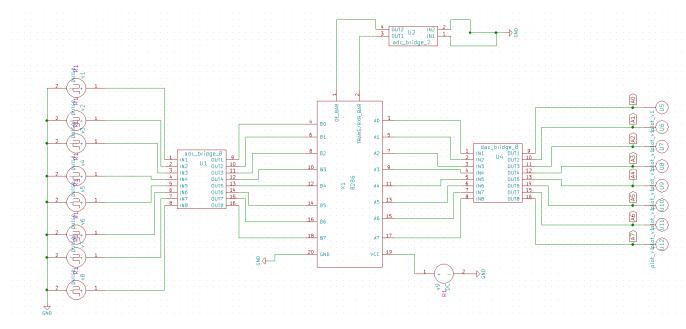

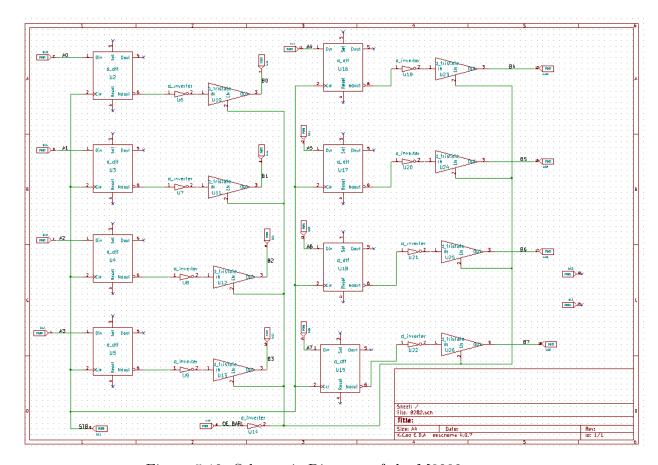

# 5.2.4 IC Schematic Diagram

Figure 5.12: Schematic Diagram of the M8282

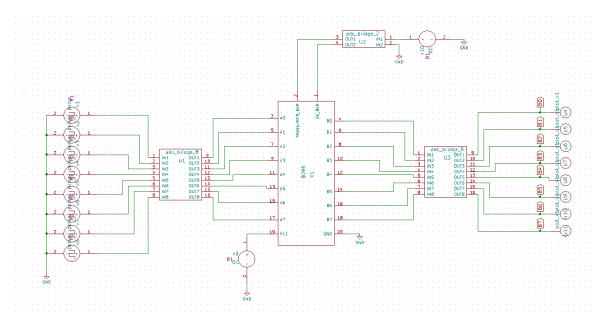

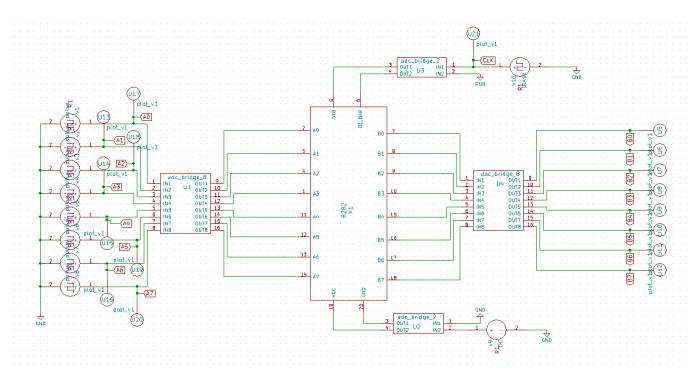

# 5.2.5 Subcircuit test circuit

Figure 5.13: Test Circuit of the M8282

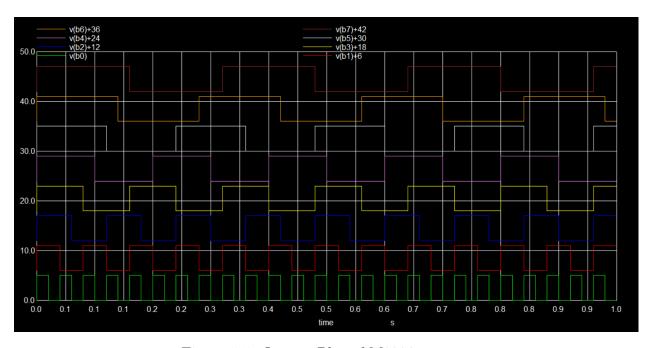

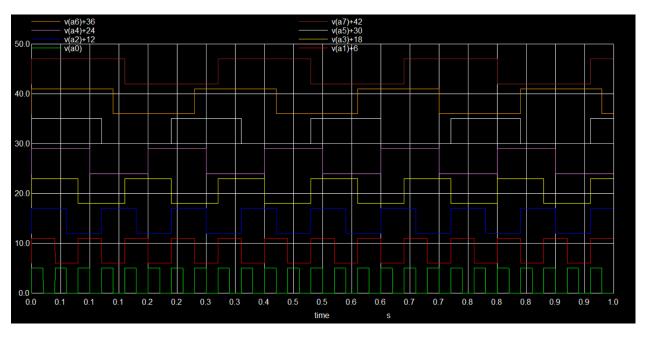

# 5.2.6 Input Plot

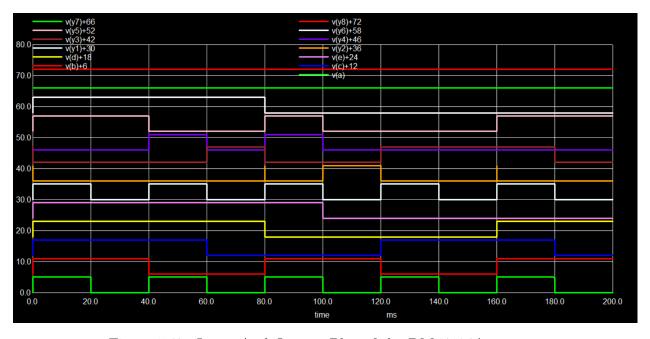

Figure 5.14: Input Plot Of M8282

# 5.2.7 Output Plot

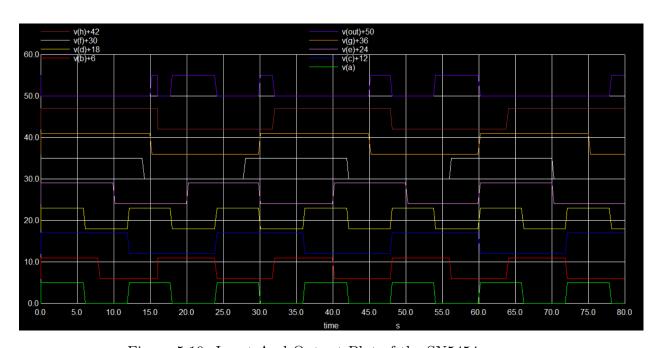

Figure 5.15: Output Plot of the M8282

#### 5.3 SN5454 4-WIDE AND-OR-INVERT GATES

The SN5454 is a dual 4-input NAND gate with standard TTL logic levels, designed for military and industrial-grade applications requiring high reliability. It performs logical NAND operations on multiple inputs and is used in control, timing, and decision-making circuits. The device supports a wide operating temperature range and is available in ceramic DIP packages for rugged environments. It is part of Texas Instruments 54-series logic family, ensuring compatibility with other TTL components. The SN5454 offers fast switching and stable performance across varied operating conditions.

Functionality: The SN5454 performs dual 4-input NAND gate logic, meaning it has two independent gates, each outputting a LOW only when all four of its inputs are HIGH. It is used to implement complex logic conditions by combining multiple input signals. The output remains HIGH for all other input combinations, making it useful for control and decision logic circuits.

$$Y = \overline{AB + CD + EF + GH}$$

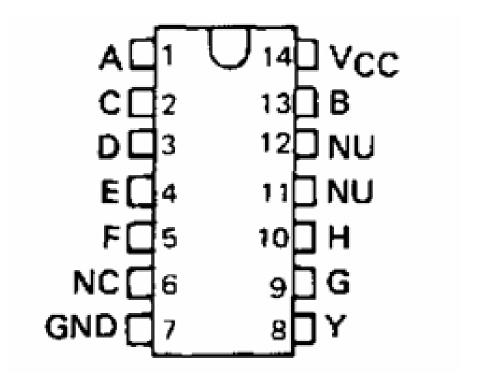

#### 5.3.1 Pin Configuration

Below is the physical package configuration for the SN5454, illustrating the pinout arrangement and mechanical layout.

Figure 5.16: Pin Configurations of the SN5454

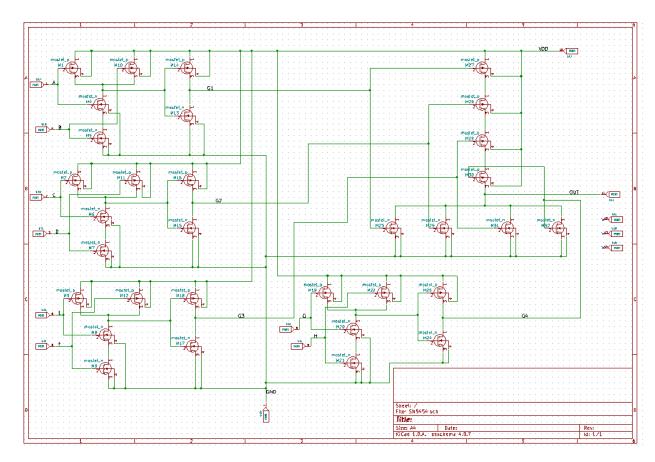

# 5.3.2 IC Schematic Diagram

Figure 5.17: Subcircuit Schematic Diagram of the  $\mathrm{SN}5454$

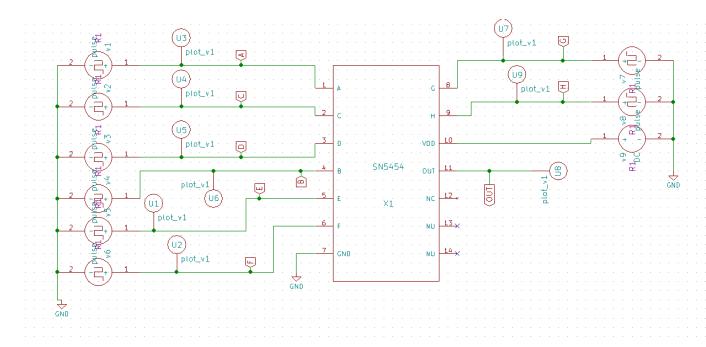

# 5.3.3 Subcircuit test circuit

Figure 5.18: Test Circuit of the SN5454

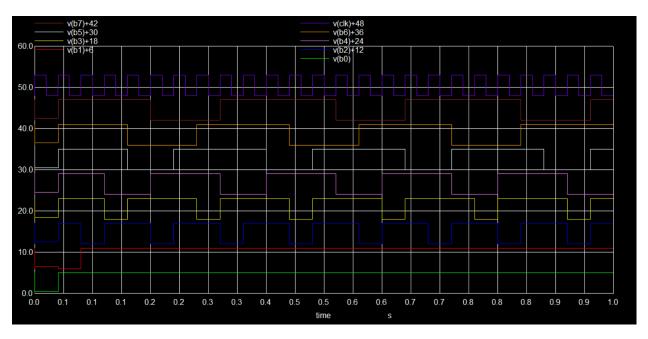

# 5.3.4 Input And Output Plot

Figure 5.19: Input And Output Plot of the SN5454

# 5.4 DM74184 BCD-to-Binary Converter

The DM54184 is a 6-bit BCD-to-binary converter IC designed using read-only memory (ROM) principles for efficient digital code conversion. It translates Binary-Coded Decimal (BCD) inputs into equivalent binary values and can also generate BCD 9's and 10's complements using dedicated outputs. Its architecture allows cascading for higher-bit conversions, and the open-collector outputs support easy interfacing. The device features an enable pin that disables the outputs when set high, minimizing power consumption. This IC is ideal for applications requiring compact and reliable numeric format conversions in digital systems.

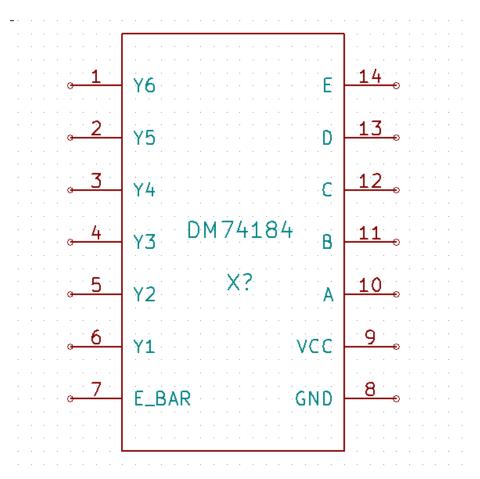

#### 5.4.1 Pin Configuration

Below is the physical package configuration for the DM54184, illustrating the pinout arrangement and mechanical layout.

Figure 5.20: Pin Configuration of the DM54184

Y6, Y5, Y4, Y3, Y2, Y1 are BCD INPUTS E, D, C, B, A are BINARY OUTPUT

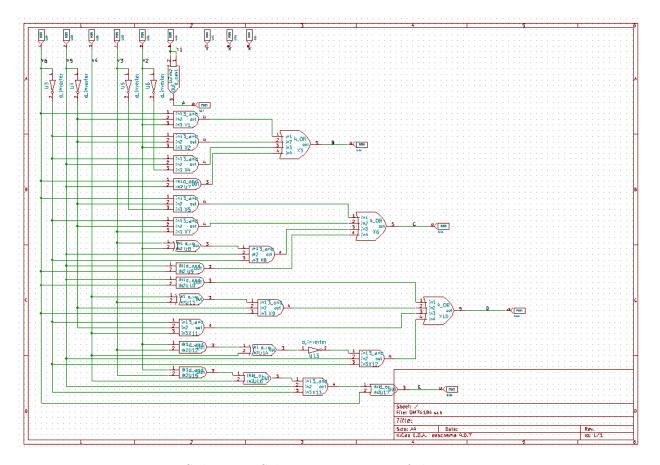

# 5.4.2 IC Schematic Diagram

Figure 5.21: Subcircuit Schematic Diagram of the DM54184

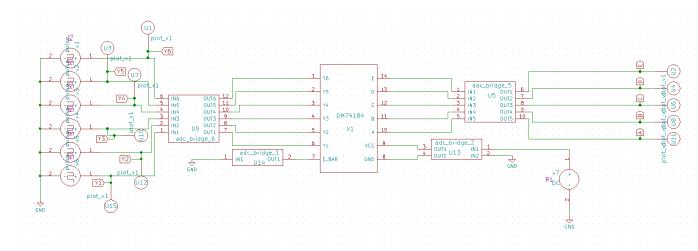

# 5.4.3 Subcircuit test circuit

Figure 5.22: Test Circuit of the DM54184

# 5.4.4 Input And Output Plot

Figure 5.23: Input And Output Plot of the DM54184

The correct binary output is produced only if the BCD combination is valid.

# 5.5 DM74185A Binary-to-BCD Converter

The DM54185A is a 6-bit binary-to-BCD (Binary-Coded Decimal) converter IC that efficiently converts binary inputs into their equivalent BCD representation. Based on ROM architecture, it enables fast and reliable digital code translation. The device supports cascading for higher-bit conversions and includes an enable input to disable outputs when not in use. Its open-collector outputs facilitate easy integration into complex digital systems. The DM54185A is ideal for applications requiring numeric data formatting in embedded and computing systems.

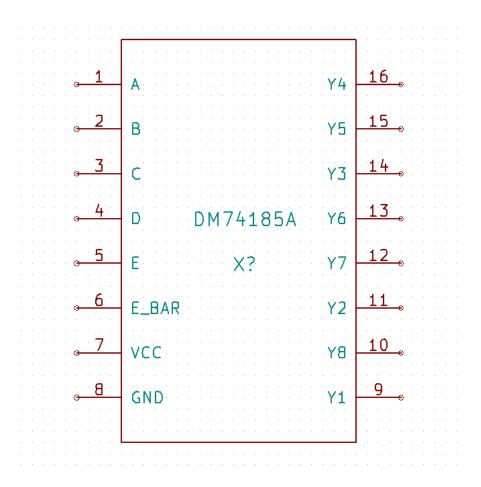

#### 5.5.1 Pin Configuration

Below is the physical package configuration for the DM54184, illustrating the pinout arrangement and mechanical layout.

Figure 5.24: Pin Configuration of the DM54185A

E, D, C, B, A are BINARY INPUT

Y8, Y7, Y6, Y5, Y4, Y3, Y2, Y1 are BCD OUTPUT

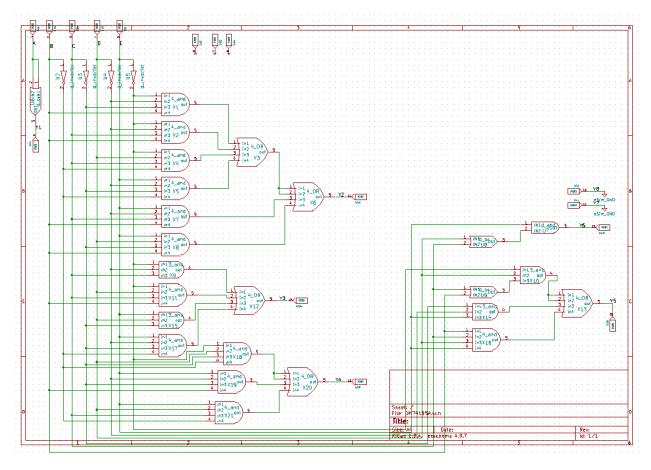

# 5.5.2 IC Schematic Diagram

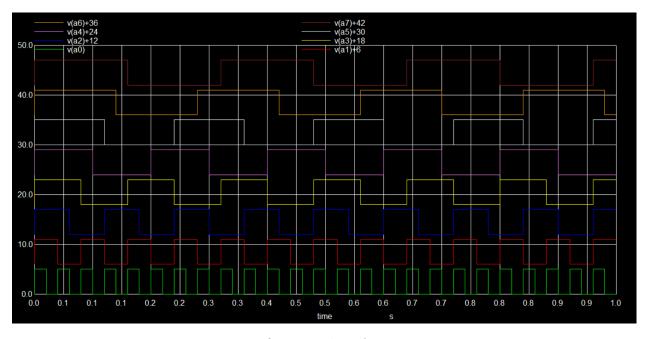

Figure 5.25: Subcircuit Schematic Diagram of the DM54185A

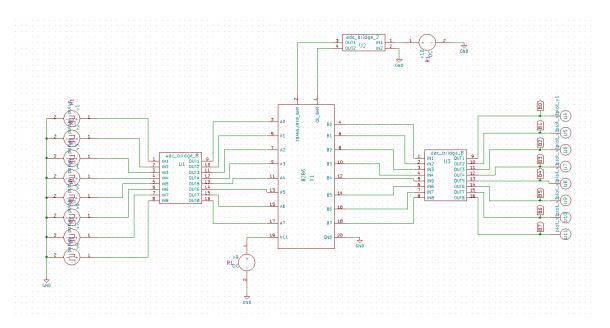

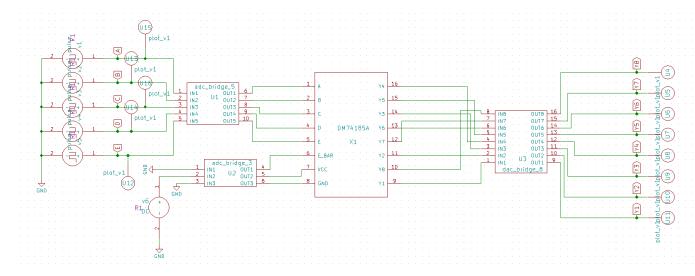

# 5.5.3 Subcircuit test circuit

Figure 5.26: Test Circuit of the DM54185A

# 5.5.4 Input And Output Plot

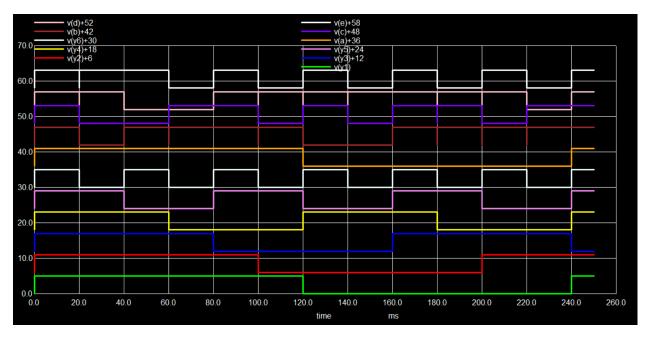

Figure 5.27: Input And Output Plot of the DM54184A

# Chapter 6

# **Device Modeling**

The Device Modeling feature of eSim allows users to create custom semiconductor device models based on datasheet parameters. Using the built-in Model Editor, users can define device parameters such as current gains, saturation currents, breakdown voltages, capacitances, and resistances. The generated models can then be integrated into the eSim library and used for circuit simulation and validation. This feature enables flexibility in simulating devices accurately as per their real-world specifications.

#### 6.1 1N914 HIGH SPEED DIODE

The 1N914 is a high-speed switching diode known for its fast reverse recovery time of 4ns, making it ideal for high-frequency and digital applications. It supports up to 100V reverse voltage and 225mA peak forward current. Housed in a compact DO-35 glass package, it's widely used for signal processing and protection tasks.

## 6.1.1 Typical Applications

- High-speed switching.

- Waveform clipping

- Fast switching rectifiers

- DC-to-DC converter circuits

#### 6.1.2 SPICE Model Implementation

#### 6.1.2.1 SPICE Model Parameters

Below is the Spice model parameter list with their corresponding Description, Values and units.

Table 6.1: SPICE Model Parameters of 1N914 HIGH SPEED DIODE

| Parameter | Description                    | Value                 | Unit |

|-----------|--------------------------------|-----------------------|------|

| IS        | Saturation current             | $2.52 \times 10^{-9}$ | A    |

| RS        | Series resistance              | 0.568                 | Ω    |

| N         | Emission coefficient           | 1.752                 | _    |

| CJO       | Zero-bias junction capacitance | 4                     | pF   |

| M         | Grading coefficient            | 0.4                   | _    |

| tt        | Transit Time                   | 20                    | ns   |

| Iave      | Average forward current        | 200                   | mA   |

| Vpk       | Peak reverse voltage           | 75                    | V    |

| MFG       | Manufacturer                   | OnSemi                | _    |

#### 6.1.2.2 SPICE Model

The Spice model for the 1N914 HIGH SPEED DIODE:

#### SPICE Model:1N914 HIGH SPEED DIODE

.model 1N914 D(Is=2.52n Rs=.568 N=1.752 Cjo=4p M=.4 tt=20n Iave=200m Vpk=75 mfg=0nSemi type=silicon)

#### 6.1.3 Device Model Characterization

The 1N914 is a High Speed Diode optimized for high-efficiency, fast-switching rectification. Its behavior is analyzed through forward and reverse bias characteristics using standard current-voltage relationships.

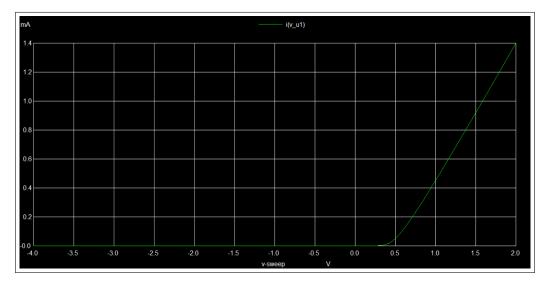

#### 6.1.3.1 Forward Bias Characteristics

In forward bias, the current through the diode follows the modified diode equation:

$$I = I_S \left( e^{\frac{qV}{nkT}} - 1 \right)$$

where  $I_S$  is the reverse saturation current, V is the forward voltage across the diode, n is the ideality factor, q is the electronic charge, k is Boltzmann's constant, and T is the absolute temperature.

The 1N914 is a fast-switching diode with a typical forward voltage drop of 0.4–1V, making it suitable for low-signal applications. Its low capacitance and quick reverse recovery enable efficient operation in high-speed and high-frequency circuits. It is widely used in logic-level switching, signal shaping, and RF paths. The forward I–V curve (Fig. X) reflects this behavior, showing a steep increase in current after threshold.

The following circuit analyzes the forward bias behavior of the 1N914 High Speed Diode. It illustrates how the diode current increases with applied forward voltage  $(V_F)$ , following the Silicon diode's exponential conduction behavior.

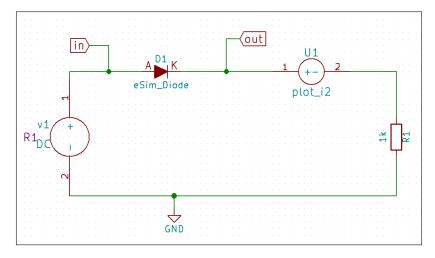

Figure 6.1: Forward bias circuit for 1N914 High Speed Diode

Below is the simulated I-V response showing the diode's low turn-on voltage and exponential current rise.

Figure 6.2: NgSpice simulation of forward I-V characteristics for 1N914

#### 6.1.3.2 Reverse Bias Characteristics

Under reverse bias, the 1N914 diode exhibits very low leakage current up to its rated reverse voltage. If the reverse voltage exceeds its maximum rating 75V, the diode may undergo avalanche breakdown, potentially leading to permanent damage. Thermal effects can also contribute to failure if power dissipation limits are exceeded. At moderate reverse voltages, the current approximates:

$$I \approx -I_S$$

The 1N914 demonstrates reliable blocking up to 75V with minimal leakage, making it ideal for reverse polarity protection and high-speed switching. The reverse I–V plot confirms stable operation with no sharp breakdown knee.

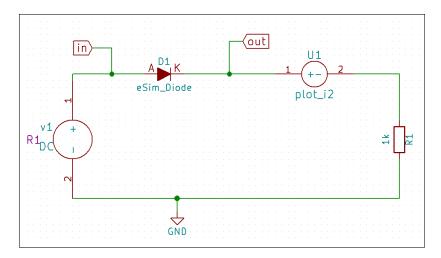

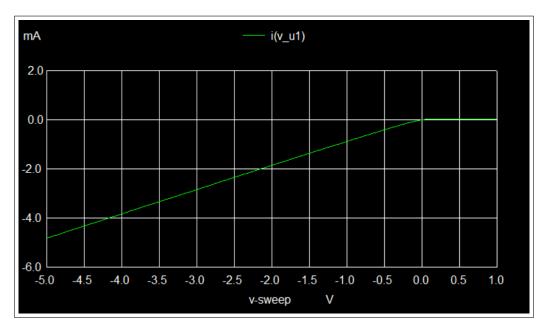

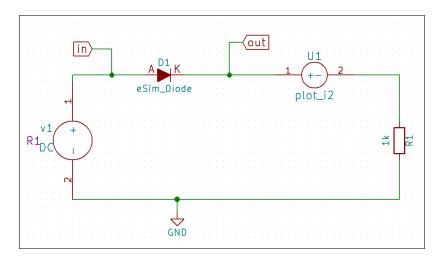

The reverse bias setup examines the leakage current and breakdown behavior of the 1N914 diode. The circuit helps study its blocking capability and reverse leakage under increasing negative voltage.

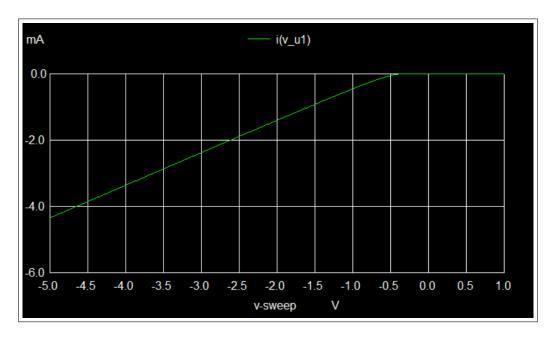

Figure 6.3: Reverse bias circuit for 1N914 High Speed diode

Simulation shows minimal leakage current until breakdown, demonstrating Schottky behavior with low reverse leakage and no avalanche effect.

Figure 6.4: NgSpice simulation of reverse I-V characteristics for 1N914

#### 6.2 1N5817 SCHOTTKY BARRIER DIODE

The 1N5817 is a Schottky barrier diode designed for low power, high-speed switching and rectification applications. It features a low forward voltage drop (typically 0.32–0.45V) and fast recovery time, making it ideal for efficient power conversion. With a maximum average forward current of 1A and reverse voltage up to 20V, it is commonly used in switched-mode power supplies and polarity protection circuits.

#### 6.2.1 Typical Applications

- Reverse polarity protection

- Low voltage rectification

- Signal demodulation

- DC-to-DC converter circuits

#### 6.2.2 SPICE Model Implementation

#### 6.2.3.1 SPICE Model Parameters

Below is the Spice model parameter list with their corresponding Description, Values and units.

Table 6.2: SPICE Model Parameters of 1N5817 Schottky Diode

| Parameter | Description                     | Value                 | Unit |

|-----------|---------------------------------|-----------------------|------|

| IS        | Saturation current              | $31.7 \times 10^{-6}$ | A    |

| RS        | Series resistance               | 0.051                 | Ω    |

| N         | Emission coefficient            | 1.373                 | _    |

| CJO       | Zero-bias junction capacitance  | 190                   | pF   |

| M         | Grading coefficient             | 0.3                   | _    |

| Iave      | Average forward current         | 1                     | A    |

| Vpk       | Peak reverse voltage            | 20                    | V    |

| EG        | Energy gap                      | 0.69                  | eV   |

| XTI       | Saturation current temp. factor | 2                     | _    |

| MFG       | Manufacturer                    | OnSemi                | _    |

#### 6.2.3.2 SPICE Model

The Spice model for the 1N5817 Schottky barrier diode:

#### SPICE Model: 1N5817 Schottky barrier diode

.model 1N5817 D(Is=31.7u Rs=.051 N=1.373 Cjo=190p M=.3 Eg=.69

Xti=2 Iave=1 Vpk=20 mfg=OnSemi type=Schottky)

#### 6.2.3 Device Model Characterization

The 1N5817 is a low forward voltage Schottky barrier diode optimized for high-efficiency, fast-switching rectification. Its behavior is analyzed through forward and reverse bias characteristics using standard current-voltage relationships.

#### 6.2.4.1 Forward Bias Characteristics

In forward bias, the current through the diode follows the modified diode equation:

$$I = I_S \left( e^{\frac{qV}{nkT}} - 1 \right)$$

where  $I_S$  is the reverse saturation current, V is the forward voltage across the diode, n is the ideality factor, q is the electronic charge, k is Boltzmann's constant, and T is the absolute temperature.

Due to its metal–semiconductor junction, the 1N5817 exhibits a lower turn-on voltage compared to PN-junction diodes, with conduction beginning at approximately 0.32–0.45V. This low forward voltage improves conduction efficiency, especially in power-sensitive and low-voltage applications. The forward I–V curve (Fig. X) reflects this behavior, showing a steep increase in current after threshold.

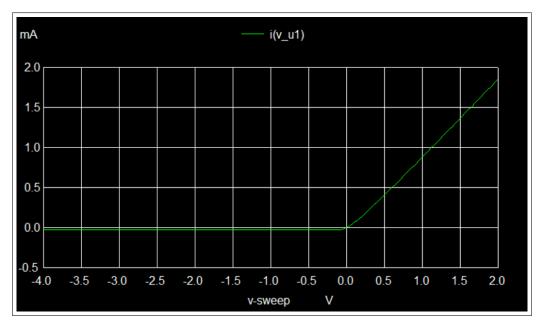

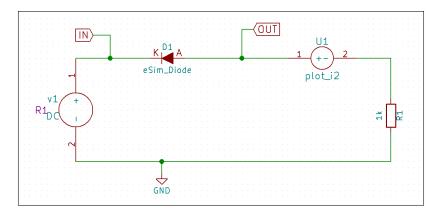

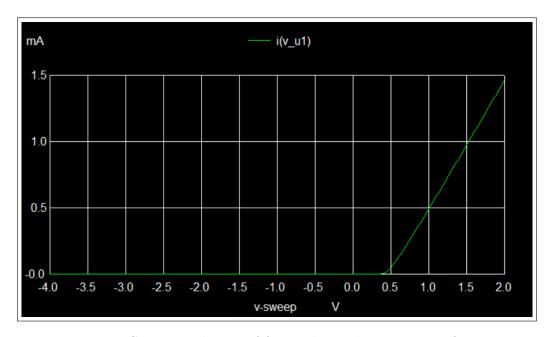

The following circuit analyzes the forward bias behavior of the 1N5817 Schottky diode. It illustrates how the diode current increases with applied forward voltage  $(V_F)$ , following the Schottky diode's exponential conduction behavior.

Figure 6.5: Forward bias circuit for 1N5817 Schottky diode

Below is the simulated I-V response showing the diode's low turn-on voltage and exponential current rise.

Figure 6.6: NgSpice simulation of forward I-V characteristics for 1N5817

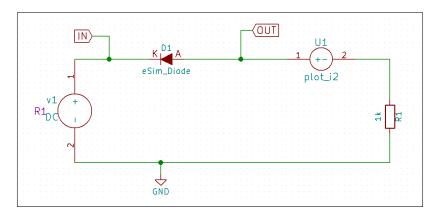

#### 6.2.4.2 Reverse Bias Characteristics

Under reverse bias, the Schottky diode maintains a small leakage current until the reverse voltage limit is reached. Unlike conventional PN-junction diodes, Schottky diodes do not undergo avalanche breakdown but may fail due to thermal effects. At moderate reverse voltages, the current approximates:

$$I \approx -I_S$$

The 1N5817 demonstrates reliable blocking up to 20V with minimal leakage, making it ideal for reverse polarity protection and high-speed switching. The reverse I–V plot confirms stable operation with no sharp breakdown knee.

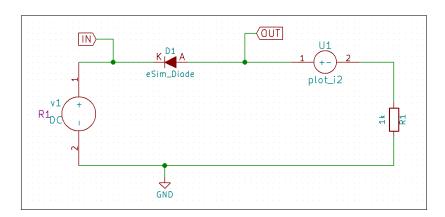

The reverse bias setup examines the leakage current and breakdown behavior of the 1N5817 diode. The circuit helps study its blocking capability and reverse leakage under increasing negative voltage.

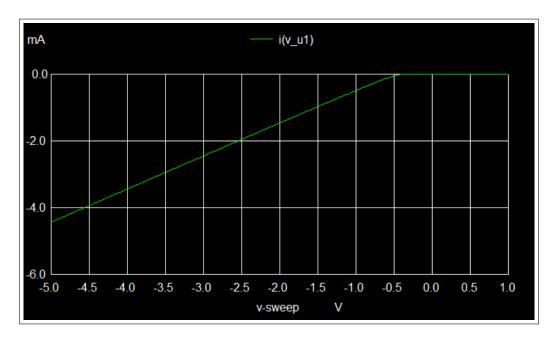

Figure 6.7: Reverse bias circuit for 1N5817 Schottky diode

Simulation shows minimal leakage current until breakdown, demonstrating Schottky behavior with low reverse leakage and no avalanche effect.

Figure 6.8: NgSpice simulation of reverse I-V characteristics for 1N5817

#### 6.3 MV2201 VARACTOR DIODE

The MV2201 is a silicon tuning diode designed for electronic tuning applications in RF and microwave circuits. It features low capacitance and a wide tuning range, making it suitable for use in voltage-controlled oscillators and frequency modulators. Its high Q factor and stable performance ensure precise frequency control. The MV2201 is commonly used in communication and signal-processing systems.

#### 6.3.1 Typical Applications

- Electronic tuning circuits

- Voltage-controlled oscillators

- RF and microwave systems

- Frequency synthesis

#### 6.3.2 SPICE Model Implementation

#### 6.3.2.2 SPICE Model Parameters

Below is the Spice model parameter list with their corresponding Description, Values and units.

Table 6.3: SPICE Model Parameters of MV2201 VARACTOR DIODE

| Parameter | Description                    | Value                   | Unit |

|-----------|--------------------------------|-------------------------|------|

| IS        | Saturation current             | $1.365 \times 10^{-12}$ | A    |

| RS        | Series resistance              | 1                       | Ω    |

| Nr        | Emission coefficient           | 2                       | _    |

| CJO       | Zero-bias junction capacitance | 14.93                   | pF   |

| M         | Grading coefficient            | 0.4261                  | _    |

| VJ        | Junction potential             | 0.75                    | V    |

| BV        | Breakdown voltage              | 25                      | V    |

| Isr       | Reverse Saturation current     | $16.02 \times 10^{-12}$ | A    |

| Ibv       | Secondary breakdown current    | $10.0 \times 10^{-6}$   | A    |

| Vpk       | Peak reverse voltage           | 25                      | V    |

| MFG       | Manufacturer                   | OnSemi                  | _    |

#### 6.3.2.2 SPICE Model

The Spice model for the MV2201 VARACTOR DIODE:

#### SPICE Model:MV2201 VARACTOR DIODE

.model MV2201 D(Is=1.365p Rs=1 Cjo=14.93p M=.4261 Vj=.75

Isr=16.02p Nr=2 Bv=25 Ibv=10u Vpk=25 mfg=OnSemi type=varactor)

#### 6.3.3 Device Model Characterization

The MV2201 is a Varactor Diode optimized for high-efficiency, fast-switching rectification. Its behavior is analyzed through forward and reverse bias characteristics using standard current-voltage relationships.

#### 6.3.3.1 Forward Bias Characteristics

In forward bias, the current through the diode follows the modified diode equation:

$$I = I_S \left( e^{\frac{qV}{nkT}} - 1 \right)$$

where  $I_S$  is the reverse saturation current, V is the forward voltage across the diode, n is the ideality factor, q is the electronic charge, k is Boltzmann's constant, and T is the absolute temperature.

The MV2201 is a silicon tuning diode designed for use in electronic tuning applications. It offers low junction capacitance and a wide tuning range, making it ideal for voltage-controlled oscillators, frequency modulators, and RF circuits. Its performance ensures precise frequency control in high-frequency systems. The forward I–V curve (Fig. X) reflects this behavior, showing a steep increase in current after threshold.

The following circuit analyzes the forward bias behavior of the MV2201 Varactor Diode. It illustrates how the diode current increases with applied forward voltage  $(V_F)$ , following the Silicon diode's exponential conduction behavior.

Figure 6.9: Forward bias circuit for MV2201 Varactor Diode

Below is the simulated I-V response showing the diode's low turn-on voltage and exponential current rise.

Figure 6.10: NgSpice simulation of forward I-V characteristics for MV2201

#### 6.3.3.2 Reverse Bias Characteristics

Under reverse bias, the MV2201 diode exhibits very low leakage current up to its rated reverse voltage of 25V. Exceeding this limit may result in breakdown and permanent damage. As a tuning diode, its primary function under reverse bias is to vary junction capacitance, not conduct current. Thermal effects may contribute to failure if power dissipation or junction temperature limits are exceeded.

$$I \approx -I_S$$

The MV2201 demonstrates reliable blocking up to 25V with minimal leakage, making it ideal for reverse polarity protection and high-speed switching. The reverse I–V plot confirms stable operation with no sharp breakdown knee.

The reverse bias setup examines the leakage current and breakdown behavior of the MV2201 diode. The circuit helps study its blocking capability and reverse leakage under increasing negative voltage.

Figure 6.11: Reverse bias circuit for MV2201 Varactor diode

Simulation shows minimal leakage current until breakdown, demonstrating Schottky behavior with low reverse leakage and no avalanche effect.

Figure 6.12: NgSpice simulation of reverse I-V characteristics for MV2201

# Chapter 7

# Conclusion and Future Scope

The project achieved its objective of developing a wide range of subcircuits for both Analog and Digital Integrated Circuits and Device Modeling, with each IC model meticulously crafted based on the specifications provided in their official datasheets. Through rigorous testing and verification using corresponding test circuits, these IC models were validated for accuracy and functionality. The components developed under this fellowship encompass fundamental circuit elements such as Operational Amplifiers (Op-Amps), Voltage Comparators, Precision Amplifiers, Bidirectional Transceivers, Octal Latch, Convertors and various Logic Gate ICs.

These models are now ready for integration into the eSim subcircuit library, providing a robust resource for developers, students, and researchers. Inclusion of these models into the eSim library will significantly enhance the capabilities of the tool, allowing users to easily incorporate these fundamental ICs into their own projects and circuit designs.

Looking ahead, this project sets the foundation for continued expansion of the eSim device model library. We anticipate that more such ready-to-use IC models will be developed, broadening the scope of available components and further empowering the eSim community. This ongoing development will not only aid in academic and research endeavors but also contribute to the growing ecosystem of open-source electronic design automation (EDA) tools.

# **Bibliography**

```

[1] FOSSEE Official Website. 2020.

URL: https://fossee.in/about

[2] eSim Official Website

URL:https://esim.fossee.in/

[3] NgSpice Official Website.

URL: https://ngspice.sourceforge.io/

[4] Makerchip Official Website

URL:https://makerchip.com/

[5] KiCad Official Website

URL:https://www.kicad.org/

[6] GHDL Official Website

URL:http://ghdl.free.fr/

[7] eSim Manual

URL:https://static.fossee.in/esim/manuals/eSim_Manual_2.4.pdf

[8] TLC2201 Adv LinCMOS LOW-NOISE PRECISION OPAMP IC

URL:https://www.ti.com/lit/ds/symlink/tlc2202m.pdf

[9] TLC271 LinCMOS PROGRAMMABLE LOW-POWER OPAMP IC

URL: https://www.ti.com/lit/ds/symlink/tlc2711b.pdf

[10] TLC272 LinCMOS PRECISION DUAL OPAMP IC

URL: https://www.ti.com/lit/ds/symlink/tlc272.pdf

[11] TLC2272 Adv LinCMOS Rail-to-Rail OPAMP IC

URL:https://www.ti.com/lit/ds/symlink/tlc2272a-ep.pdf

```

- [12] TLV2221 Adv LinCMOS VERY LOW-POWER SINGLE OPAMP IC URL:https://www.ti.com/lit/ds/symlink/tlv2221.pdf

- [13] TLV2211 Adv LinCMOS Rail-to-Rail MICROPOWER OPAMP URL:https://www.ti.com/lit/ds/symlink/tlv2211.pdf

- [14] NJU7031 LOW VOLTAGE CMOS OPAMP IC URL:https://www.mouser.com/datasheet/2/294/njr\_nju7031\_nju7032\_ nju7034\_e-1187474.pdf

- [15] NJU7108 LOW POWER And LOW OFFSET VOLTAGE CMOS COMPARA-TOR URL:https://www.mouser.com/datasheet/2/294/NJU7108\_E-1710815.pdf

- [16] NJU7091A LOW POWER And LOW OFFSET VOLTAGE CMOS OPAMP IC URL:https://www.mouser.com/datasheet/2/294/NJU7091A\_NJU7092A\_ NJU7093A\_E-1917646.pdf

- [17] ICL7660 VOLTAGE CONVERTERS

URL:https://www.renesas.com/en/document/dst/icl7660-datasheet

- [18] M8286 Bidirectional Bus Transceiver URL:https://www.silicon-ark.co.uk/datasheets/m8286-m8287-datasheet-intel.pdf

- [19] M8282 OCTAL LATCH

URL: https://www.alldatasheet.com/datasheet-pdf/view/128951/INTEL/

8282.html

- [20] SN5454 4-WIDE AND-OR-INVERT GATES

URL:https://www.ti.com/lit/ds/symlink/sn541s54.pdf

- [21] DM74184 BCD-to-Binary Converter URL: https://digsys.upc.edu/csd/chips/classic/DM74185.pdf

- [22] DM74185A Binary-to-BCD Converter URL: https://digsys.upc.edu/csd/chips/classic/DM74185.pdf

- [23] 1N914 HIGH SPEED DIODES

URL: https://wp.optics.arizona.edu/mnofziger/wp-content/uploads/

sites/31/2016/08/1N914.pdf

URL: https://www.onsemi.com/download/data-sheet/pdf/1n914-d.pdf

#### [24] 1N5817 SCHOTTKY BARRIER DIODES

URL:https://global.oup.com/us/companion.websites/fdscontent/

uscompanion/us/pdf/microcircuits/students/diode/1n5817-philip.pdf

#### [25] MV2201 VARACTOR DIODE

$$\label{linear_could} \begin{split} URL: & \texttt{https://www.silicon-ark.co.uk/datasheets/mv2201-mv2209-datasheet-motorola.pdf} \end{split}$$