## Semester Long Internship Report

On

# Integrated Circuit Design using Subcircuit Feature of eSim

Submitted by

## Subikeesh M

Under the guidance of

## Prof. Kannan M. Moudgalya

Chemical Engineering Department IIT Bombay

June 12, 2025

## Acknowledgment

We extend our sincere gratitude to the **FOSSEE**, **IIT Bombay** team for providing us with this incredible opportunity to work on designing and integrating multiple sub-circuits in eSim. This experience has been immensely valuable, giving us hands-on exposure to open-source EDA tools for circuit simulation and a deeper understanding of their real-world applications.

We are profoundly grateful to **Prof. Kannan M. Moudgalya** for his unwavering support and guidance throughout this fellowship. Our heartfelt thanks also go to our mentors, **Mr. Sumanto Kar, Ms. Usha Vishwanathan**, and **Ms. Vineeta Ghavri**, whose expertise and continuous encouragement helped us overcome challenges and successfully complete our project.

This internship has been a transformative learning experience, equipping us with crucial skills and insights that will be invaluable in our future careers. Being part of the **FOSSEE** initiative has been a truly rewarding journey, and we deeply appreciate the knowledge and practical exposure we have gained. As aspiring professionals in the semiconductor field, we consider this internship a significant milestone in our professional growth.

## Contents

| 1 | $\mathbf{Intr}$ | roduction                    |

|---|-----------------|------------------------------|

|   | 1.1             | eSim                         |

|   | 1.2             | NgSpice                      |

|   | 1.3             | Makerchip                    |

| 2 | Feat            | tures of eSim                |

| 3 | Abs             | etract 9                     |

| • | 3.1             | Approach                     |

| 4 | SN5             | 54LS06                       |

| 4 | 4.1             | General Description          |

|   | 4.2             | Key Features                 |

|   | 4.3             | Applications                 |

|   | 4.4             | Pin Configuration            |

|   | 4.5             | IC Layout                    |

|   | 4.6             | Subcircuit Schematic Diagram |

|   | 4.7             | Test Circuit                 |

|   | 4.8             | Input Plot                   |

|   | 4.9             | Output Plot                  |

| 5 | CNE             | 54LS10                       |

| J | 5.1             | General Description          |

|   | 5.1             | Key Features                 |

|   | 5.2             | Applications                 |

|   | 5.4             | Pin Configuration            |

|   | 5.5             | IC Layout                    |

|   | 5.6             | Subcircuit Shematic Diagram  |

|   | 5.7             | Subcircuit Single Unit       |

|   | 5.8             | Test Circuit                 |

|   | 5.9             | Input Plot                   |

|   | 5.10            |                              |

| 6 | SN5             | 54LS11 20                    |

| U | 6.1             | General Description          |

|   | 6.2             | Key Features                 |

|   | 6.3             | Applications                 |

|   | 6.4             | Pin Configuration            |

|   | 6.5             | IC Layout                    |

|   | 6.6             | Subcircuit Schematic         |

|   | 6.7             | Subcircuit Single Unit       |

|   | 6.8             | Test Circuit                 |

|   | 6.9             | Input Plot                   |

| 7  |             |                                  |   |  |  |  |

|----|-------------|----------------------------------|---|--|--|--|

|    | 7.1         | General Description              |   |  |  |  |

|    | 7.2         | Key Features                     |   |  |  |  |

|    | 7.3         | Applications                     |   |  |  |  |

|    | 7.4         | Pin Configuration                | 7 |  |  |  |

|    | 7.5         | IC Layout                        | 7 |  |  |  |

|    | 7.6         | Subcircuit Schematic             | 8 |  |  |  |

|    | 7.7         | Subcircuit Single Unit           | 8 |  |  |  |

|    | 7.8         | Test Circuit                     | 9 |  |  |  |

|    | 7.9         | Input Plot                       | 9 |  |  |  |

|    | 7.10        | Output Plot                      | 1 |  |  |  |

| 8  | CNIE        | $4\mathrm{LS}15$                 | 2 |  |  |  |

| ð  | 8.1         |                                  |   |  |  |  |

|    |             | 1                                |   |  |  |  |

|    | 8.2         | v                                |   |  |  |  |

|    | 8.3         | Applications                     |   |  |  |  |

|    | 8.4         | Pin Configuration                |   |  |  |  |

|    | 8.5         | IC Layout                        |   |  |  |  |

|    | 8.6         | Subcircuit Single Unit Schematic |   |  |  |  |

|    | 8.7         | Test Circuit                     |   |  |  |  |

|    | 8.8         | Input And Output Plot            | 4 |  |  |  |

| 9  | SN5         | 4LS51 3                          | 7 |  |  |  |

|    | 9.1         | General Description              |   |  |  |  |

|    | 9.2         | Key Features                     |   |  |  |  |

|    | 9.3         | Applications                     |   |  |  |  |

|    | 9.4         | Pin Configuration                |   |  |  |  |

|    | 9.5         | IC Layout                        |   |  |  |  |

|    | 9.6         | Subcircuit Schematic             |   |  |  |  |

|    | 9.7         | Test Circuit                     |   |  |  |  |

|    | 9.8         | Input And Output Plot            |   |  |  |  |

|    | <i>0</i> .0 | imput find Output Flot           | 0 |  |  |  |

| 10 |             | 4LS01                            |   |  |  |  |

|    |             | General Description              |   |  |  |  |

|    |             | Key Features                     | 4 |  |  |  |

|    |             | Applications                     | 4 |  |  |  |

|    |             | Pin Configuration                | 5 |  |  |  |

|    |             | IC Layout                        | 5 |  |  |  |

|    | 10.6        | Subcircuit Schematic             | 6 |  |  |  |

|    | 10.7        | Test Circuit                     | 6 |  |  |  |

|    | 10.8        | Input Plot 1                     | 7 |  |  |  |

|    | 10.9        | Input Plot 2                     | 7 |  |  |  |

|    | 10.10       | Output Plot                      | 8 |  |  |  |

| 11 | SN5         | 404                              | ^ |  |  |  |

| 11 |             | General Description              | _ |  |  |  |

|    |             | 1                                |   |  |  |  |

|    |             | Key Features                     | - |  |  |  |

|    |             | Applications                     |   |  |  |  |

|    |             | Pin Configuration                | _ |  |  |  |

|    |             | IC Layout                        |   |  |  |  |

|    |             | Single Unit Subcircuit Schematic |   |  |  |  |

|    |             | Test Circuit                     |   |  |  |  |

|    |             | Input Plot                       |   |  |  |  |

|    | 11.9        | Output Plot                      | 2 |  |  |  |

| $12~\mathrm{SN}5405$                  |            |  |  |  |  |

|---------------------------------------|------------|--|--|--|--|

| 12.1 General Description              | 53         |  |  |  |  |

| 12.2 Key Features                     | 53         |  |  |  |  |

| 12.3 Applications                     | 53         |  |  |  |  |

| 12.4 Pin Configuration                | 54         |  |  |  |  |

| 12.5 IC Layout                        | 54         |  |  |  |  |

| 12.6 Single Unit Subcircuit Schematic | 55         |  |  |  |  |

| 12.7 Test Circuit                     | 55         |  |  |  |  |

| 12.8 Input Plot                       | 56         |  |  |  |  |

| 12.9 Output Plot                      | 56         |  |  |  |  |

|                                       |            |  |  |  |  |

|                                       | <b>57</b>  |  |  |  |  |

|                                       | 57         |  |  |  |  |

|                                       | 57         |  |  |  |  |

|                                       | 57         |  |  |  |  |

| 3 3 3 3 3                             | 58         |  |  |  |  |

| v                                     | 58         |  |  |  |  |

|                                       | 59         |  |  |  |  |

|                                       | 59         |  |  |  |  |

| I                                     | 60         |  |  |  |  |

|                                       | 60         |  |  |  |  |

| 13.10Output Plot                      | 61         |  |  |  |  |

|                                       | 20         |  |  |  |  |

|                                       | 6 <b>2</b> |  |  |  |  |

|                                       | 62         |  |  |  |  |

| ·                                     | 62         |  |  |  |  |

| 14.3 Test Circuit                     | 63         |  |  |  |  |

| 15 Conclusion and Future Scope 64     |            |  |  |  |  |

| 16 Circuits Contribution              | 65         |  |  |  |  |

| 16.1 Subikeesh M List of ICs          | 65         |  |  |  |  |

## Introduction

#### FOSSEE and eSim: Pioneering Open-Source EDA Solutions

The Free/Libre and Open Source Software for Education (FOSSEE) project, headquartered at IIT Bombay, is a significant initiative under the National Mission on Education through Information and Communication Technology (ICT), Ministry of Education, Government of India. Its primary mission is to minimize dependence on proprietary software in academia by advocating for the adoption of open-source alternatives.

One of FOSSEE's flagship projects is **eSim**, an open-source Electronic Design Automation (EDA) tool tailored for circuit design, simulation, analysis, and PCB design. eSim integrates various open-source software packages, including KiCad, Ngspice, GHDL, OpenModelica, Verilator, Makerchip, and the SkyWater SKY130 Process Design Kit (PDK). This integration offers users a comprehensive platform for designing and simulating electronic circuits without the financial burden associated with proprietary tools.

eSim provides a range of features:

- Schematic Creation: Utilize KiCad's eeschema editor to craft and modify circuit schematics.

- PCB Layout Design: Design intricate PCB layouts and generate Gerber files using KiCad's cvpcb package.

- Simulation and Analysis: Convert KiCad netlists to Ngspice netlists for detailed circuit simulation and analysis.

- Mixed-Signal Simulation: Incorporate both analog and digital components in simulations, facilitated by tools like GHDL and Verilator.

- Model and Subcircuit Builder: Add or edit device models and subcircuits seamlessly.

- Cross-Platform Support: Compatible with both Ubuntu and Windows operating systems.

Through eSim, FOSSEE empowers educational institutions, researchers, and industry professionals to transition from expensive proprietary EDA tools to a cost-effective, open-source solution, thereby fostering innovation and collaboration in the field of electronic design.

#### 1.1 eSim

eSim, created by the FOSSEE project at IIT Bombay, is a versatile open-source software tool for circuit design and simulation. It combines various open-source software packages into one cohesive platform, making it easier to design, simulate, and analyze electronic circuits. This tool is particularly useful for students, educators, and professionals who need an affordable and accessible alternative to proprietary software.

eSim offers features for schematic creation, circuit simulation, and PCB design, and includes an extensive library of components. The Subcircuit feature is a significant enhancement, enabling users to design complex circuits by integrating simpler subcircuits. Through eSim, FOSSEE promotes the use of open-source solutions in engineering education and professional fields, encouraging innovation and collaboration.

#### 1.2 NgSpice

NgSpice is an open-source SPICE simulator for electric and electronic circuits. It can simulate various circuit elements, including JFETs, bipolar and MOS transistors, passive elements (R, L, C), diodes and other devices, all interconnected in a netlist.

Digital circuits are also simulated, ranging from single gates to complex circuits, including combinations of analog, digital, and mixed-signal circuits. NgSpice offers a wealth of device models for active, passive, analog, and digital elements. Users input their circuits as netlists, and the output is one or more graphs of currents, voltages, and other electrical quantities, or saved in a data file

#### 1.3 Makerchip

Makerchip is a platform that offers convenient and accessible tools for digital circuit design. It provides both browser-based and desktop-based environments for coding, compiling, simulating, and debugging Verilog designs. Makerchip supports a combination of open-source and proprietary tools, ensuring a comprehensive range of capabilities.

Users can simulate Verilog/SystemVerilog/Transaction-Level Verilog code in Makerchip. eSim is interfaced with Makerchip using a Python-based application called Makerchip-App, which launches the Makerchip IDE. Makerchip aims to make circuit design easy and enjoyable for users of all skill levels. The platform provides a userfriendly interface, intuitive workflows, and a range of helpful features that simplify the design process and enhance the overall user experience.

The main drawback of these open-source tools is that they are not comprehensive. While some are capable of PCB design (e.g., KiCad), others focus on simulations (e.g., gEDA). To the best of our knowledge, there is no open-source software that combines circuit design, simulation, and layout design in one platform. eSim addresses this gap by integrating all these capabilities.

## Features of eSim

The objective behind the development of eSim is to provide an open-source EDA solution for electronics and electrical engineers. The software is capable of performing schematic creation, PCB design, and circuit simulation (analog, digital, and mixedsignal). It also provides facilities to create new models and components. Thus, eSim offers the following features:

- 1. Schematic Creation: eSim provides an easy-to-use graphical interface for drawing circuit schematics, making it accessible for users of all levels. Users can drag and drop components from the library onto the schematic, simplifying the design process. Comprehensive editing tools allow for easy modification of schematics, including moving, rotating, and labeling components.

- 2. Circuit Simulation: eSim supports SPICE (Simulation Program with Integrated Circuit Emphasis), a standard for simulating analog and digital circuits. Users can perform various types of analysis such as transient, AC, and DC, providing insights into circuit behavior over time and frequency. An integrated waveform viewer helps visualize simulation results, aiding in the analysis and debugging of circuit designs.

- **3. PCB Design:** The PCB layout editor allows users to place components and route traces with precision. eSim includes DRC (Design Rule Check) capabilities to ensure that the PCB design adheres to manufacturing constraints and electrical rules. Users can generate Gerber files, which are standard for PCB fabrication, directly from their designs.

- 4. Subcircuit Feature: This feature enables users to create complex circuits by integrating smaller, simpler subcircuits, promoting modular and hierarchical design approaches. Subcircuits can be reused in different projects, saving time and effort in redesigning common circuit elements.

- 5. Open Source Integration: eSim integrates several open-source tools like KiCad, NgSpice, and GHDL, providing a comprehensive suite for electronic design automation. Being open-source, eSim is free to use, making advanced circuit design tools accessible without the need for expensive licenses.

## Abstract

The objective of this internship was to design and develop various integrated circuits (ICs) using the Subcircuit Builder Method in eSim. This involved modeling the ICs with eSim library files and subsequently simulating them with different circuits. The goal was to expand the eSim Subcircuit Library for future use, enhancing its utility and application in both educational and practical scenarios.

#### 3.1 Approach

- Identify and research an integrated circuit (IC) that is not currently available in the eSim library.

- Obtain and study the datasheet of the selected IC thoroughly.

- Carefully examine the schematic provided in the datasheet.

- Accurately recreate the schematic in eSim using the Subcircuit Builder Method.

- Model the IC in eSim, ensuring all parameters and configurations match those in the datasheet.

- Simulate the integrated circuit within eSim, testing it with various circuits to verify its functionality.

- Document the process and results to contribute to the future use and expansion of the eSim Subcircuit Library.

If the simulated outputs deviated from expected results, it signaled potential errors in the schematic. In such instances, we revisited the design phase to identify and correct discrepancies. The iterative process of debugging and re-testing continued until the test cases produced satisfactory results. Once the IC models met the desired performance criteria, they were deemed successful, marking the completion of the design process

## **SN54LS06**

#### 4.1 General Description

The SN54LS06 hex inverters feature high-voltage open-collector outputs designed for interfacing with high-level circuits or driving high-current loads. These devices can operate with output voltages up to 30 V and can sink up to 40 mA per output. Inputs are compatible with standard TTL logic levels, making them suitable for easy interfacing with TTL families. The SN54LS06 series is characterized for use over a wider temperature range, typically from –55°C to 125°C, making them suitable for military and industrial applications. These devices also feature clamped inputs to reduce transmission-line effects and simplify system design.

#### 4.2 Key Features

- High-Voltage Output Capability: Can sink current from up to 30 V external supplies.

- TTL-Compatible Inputs: Designed to interface seamlessly with other TTL logic circuits.

- High Output Current Capability: Each output can sink up to 40 mA.

- Wide Operating Temperature Range: From -55°C to 125°C, ideal for military and industrial environments.

#### 4.3 Applications

- Lamp and LED Driving: Used to drive indicators and display elements requiring higher voltages or currents.

- Relay Driving: Suitable for controlling small relays directly.

- Logic Level Shifting: Enables shifting TTL logic levels to higher voltages for driving other devices.

- Buffering and Isolation: Used to isolate logic circuits from noisy or high-power circuits.

#### 4.4 Pin Configuration

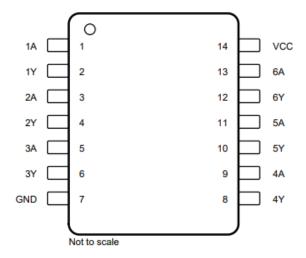

Figure 4.1: Pin of SN54LS06

#### 4.5 IC Layout

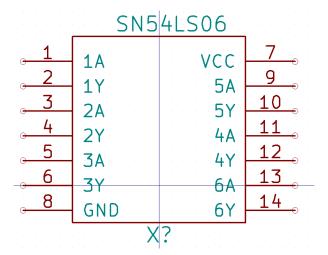

Figure 4.2: Layout of SN54LS06

## 4.6 Subcircuit Schematic Diagram

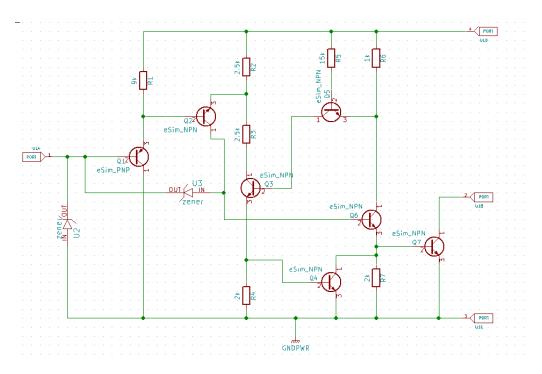

Figure 4.3: Subcircuit Schematic of SN54LS06

#### 4.7 Test Circuit

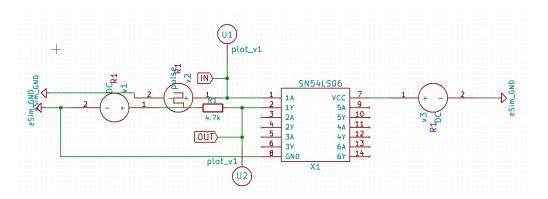

Figure 4.4: Test Circuit of SN54LS06

#### 4.8 Input Plot

Figure 4.5: Input Plot

#### 4.9 Output Plot

Figure 4.6: Output Plot

## **SN54LS10**

#### 5.1 General Description

The SN54LS10 is a triple 3-input positive-NAND gate designed to perform the logical NAND operation. It is a member of the standard TTL logic family, providing high-speed logic operation with low power dissipation. The device features standard TTL-compatible inputs and outputs, making it easy to interface with other TTL circuits. The SN54LS10 is characterized for operation over the military temperature range from -55°C to 125°C, making it suitable for demanding industrial and defense applications. Typical propagation delay time is about 10 ns, and typical power dissipation is around 33 mW per gate.

#### 5.2 Key Features

- Three 3-Input NAND Gates: Provides versatility in logic design by combining multiple signals.

- TTL-Compatible Inputs and Outputs: Ensures easy interfacing with other standard TTL devices.

- High Noise Immunity: Reliable operation even in noisy environments.

- Wide Operating Temperature Range: From -55°C to 125°C, suitable for military and industrial applications.

#### 5.3 Applications

- Logic Function Implementation: Used to build complex logic circuits by combining multiple NAND gates.

- Signal Control and Gating: Allows control of multiple signals based on specific logic conditions.

- Pulse and Timing Circuits: Suitable for use in timing and control logic applications.

- General Purpose Logic: Widely used in digital systems requiring NAND logic functionality.

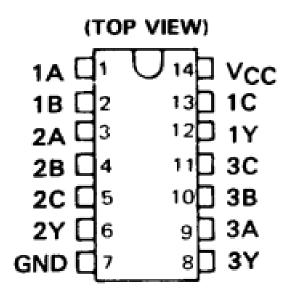

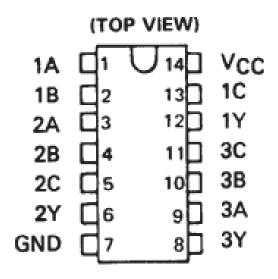

#### 5.4 Pin Configuration

Figure 5.1: Pin Configuration oof SN54LS10  $\,$

#### 5.5 IC Layout

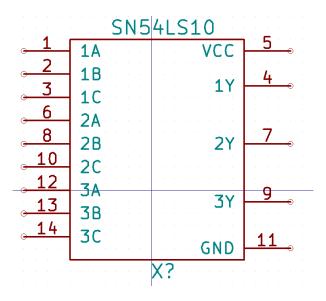

Figure 5.2: IC Layout of SN54LS10

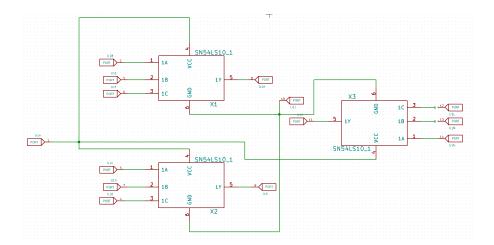

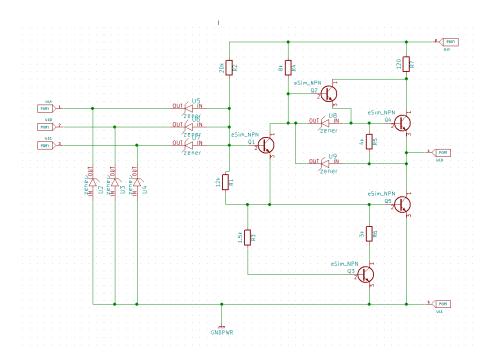

## 5.6 Subcircuit Shematic Diagram

Figure 5.3: Subcircuit of SN54LS10

## 5.7 Subcircuit Single Unit

Figure 5.4: Single Unit of SN54LS10

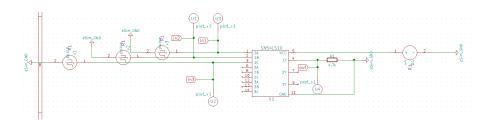

#### 5.8 Test Circuit

Figure 5.5: Test Circuit of SN54LS10

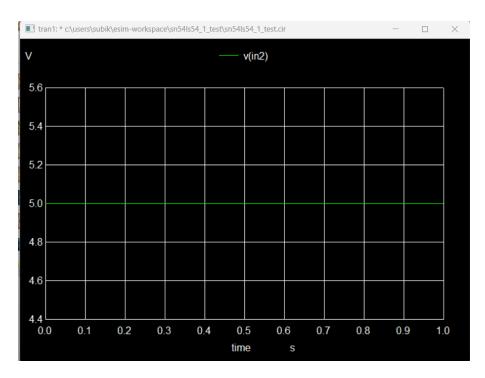

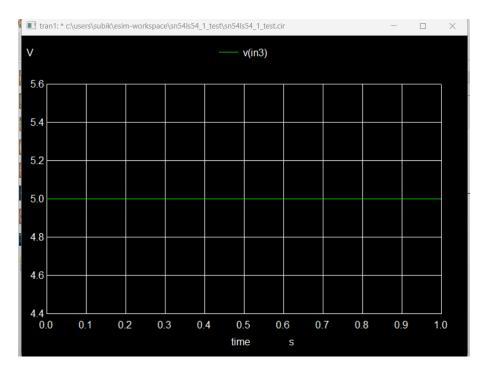

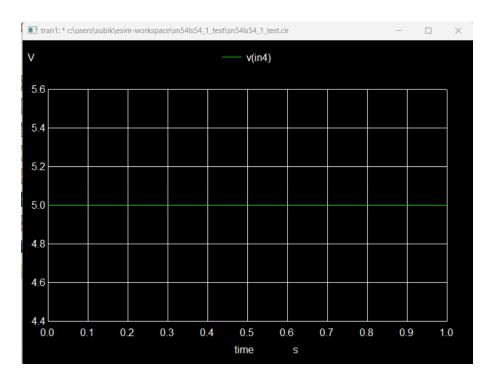

## 5.9 Input Plot

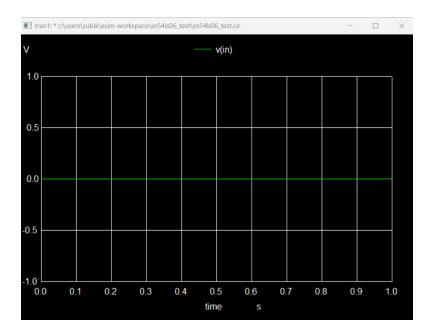

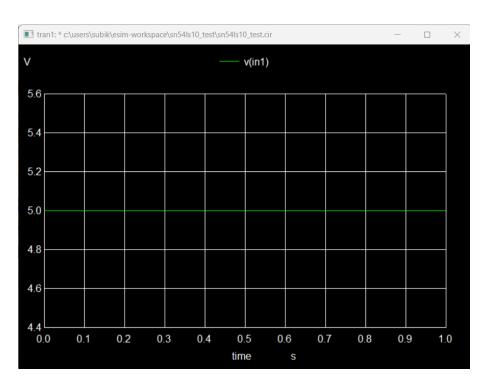

Figure 5.6: Input Plot

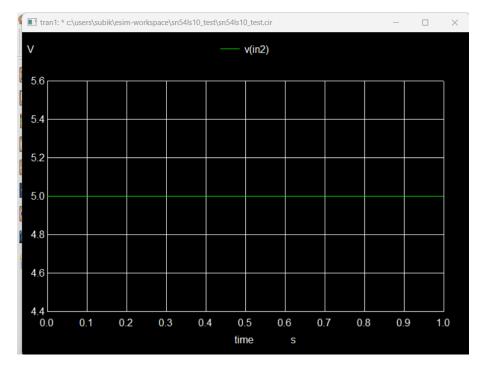

Figure 5.7: Input Plot

Figure 5.8: Input Plot

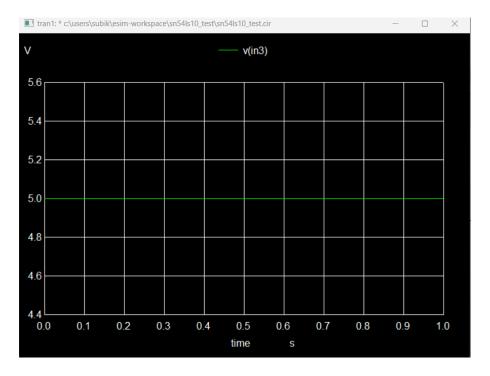

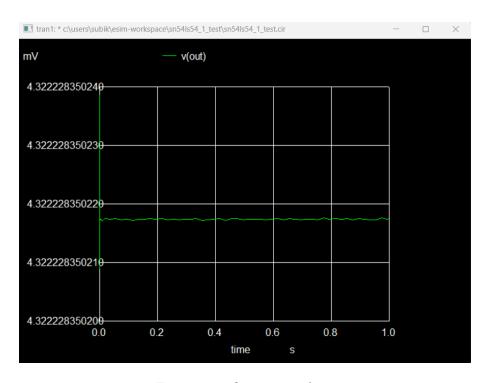

#### 5.10 Output Plot

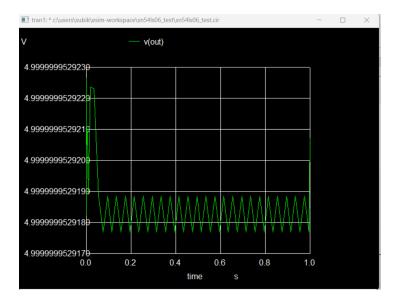

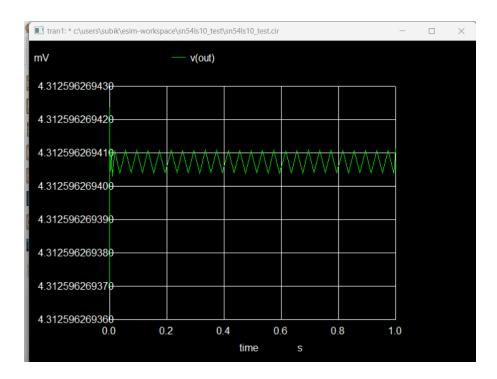

Figure 5.9: Output Plot

## SN54LS11

#### 6.1 General Description

The SN54LS11 is a triple 3-input positive-AND gate device, designed to perform logical AND operations on three inputs per gate. It belongs to the TTL (Transistor-Transistor Logic) family, offering high-speed switching and low power consumption. Each gate outputs a high logic level only when all three inputs are high. The SN54LS11 is characterized for operation over the military temperature range from  $-55^{\circ}$ C to 125°C, making it well-suited for military and industrial applications where robust performance is required. Typical propagation delay is around 10 ns, and power dissipation is approximately 33 mW per gate.

#### 6.2 Key Features

- Three 3-Input AND Gates: Combines three input signals to provide logical AND functionality.

- TTL-Compatible Inputs and Outputs: Easily interfaces with other standard TTL devices.

- High Noise Immunity: Ensures stable operation in electrically noisy environments.

- Wide Operating Temperature Range: From -55°C to 125°C, making it suitable for military-grade and industrial use.

#### 6.3 Applications

- Logic Function Implementation: Used to perform multi-input logic decisions in digital systems.

- Signal Gating and Control: Controls signal flow based on multiple logic conditions.

- Data Routing and Enable Circuits: Commonly used to enable or disable signals when specific conditions are met.

- Timing and Synchronization Circuits: Useful in circuits requiring precise logical timing and synchronization.

#### 6.4 Pin Configuration

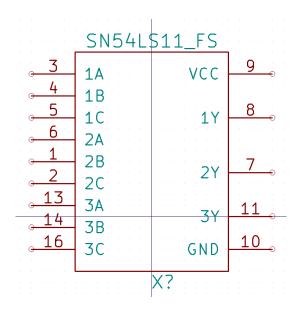

Figure 6.1: Pin Configuration of SN54LS11

#### 6.5 IC Layout

Figure 6.2: IC Layout of SN54LS11

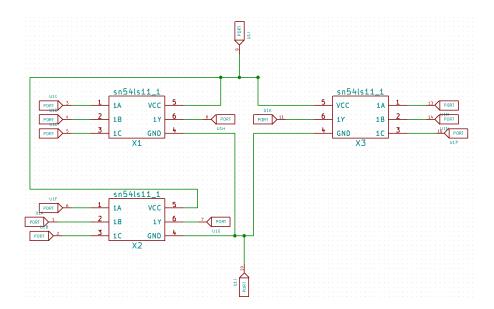

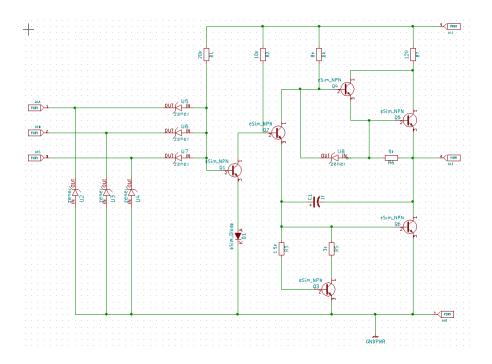

#### 6.6 Subcircuit Schematic

Figure 6.3: Subcircuit of SN54LS11

## 6.7 Subcircuit Single Unit

Figure 6.4: Single Unit of SN54LS11  $\,$

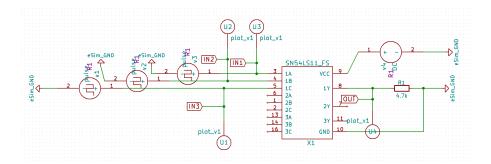

#### 6.8 Test Circuit

Figure 6.5: Test Circuit of SN54LS11

#### 6.9 Input Plot

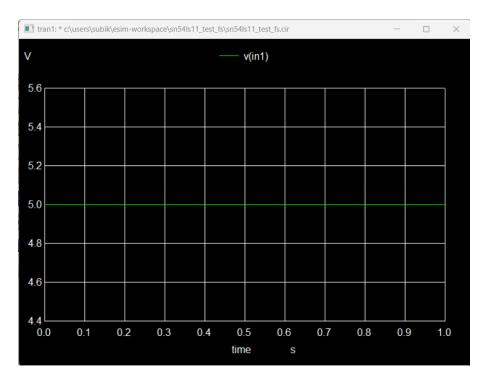

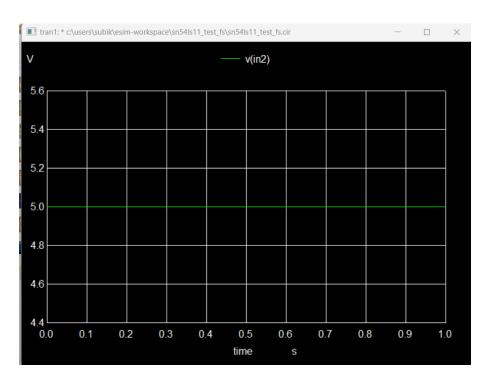

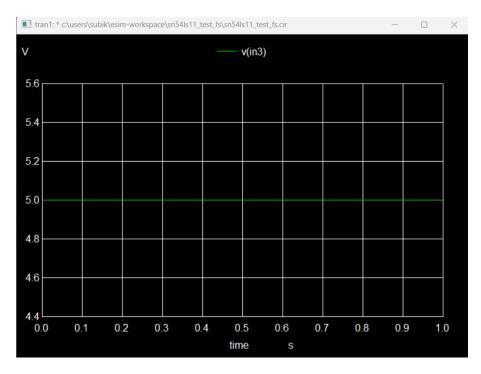

Figure 6.6: Input Plot

Figure 6.7: Input Plot

Figure 6.8: Input Plot

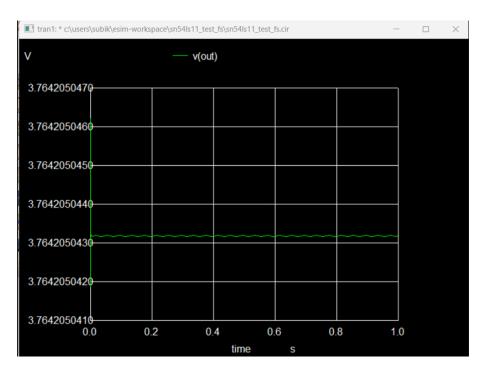

Figure 6.9: Output Plot

## SN54LS12

#### 7.1 General Description

The SN54LS12 is a dual 4-input positive-NAND gate with open-collector outputs. Unlike standard NAND gates with totem-pole outputs, the open-collector configuration allows these gates to sink higher currents and enables wired-AND connections for multiple outputs. This makes them especially suitable for driving LEDs, lamps, or other loads requiring higher current. The SN54LS12 is a member of the TTL logic family and is characterized for operation over the wide military temperature range from -55°C to 125°C. Typical propagation delay is around 15 ns, and the maximum output sink current can reach 40 mA.

#### 7.2 Key Features

- Two 4-Input NAND Gates: Provides logic flexibility by combining four input signals in each gate.

- Open-Collector Outputs: Allows wired-AND connections and higher current sinking capabilities.

- TTL-Compatible Inputs: Simplifies interfacing with other TTL logic circuits.

- Wide Operating Temperature Range: From -55°C to 125°C, suitable for military and industrial applications.

#### 7.3 Applications

- **LED and Lamp Driving:** Can directly drive indicator lamps and LEDs due to its open-collector output.

- Relay Control: Suitable for controlling relays or other high-current loads.

- Logic Expansion: Enables wired-AND logic by connecting multiple outputs together.

- Signal Gating and Control: Used for complex logic gating functions requiring multiple input conditions.

#### 7.4 Pin Configuration

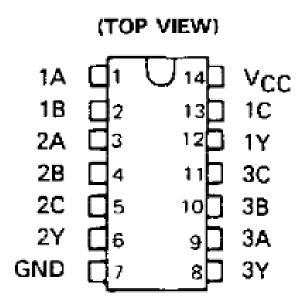

Figure 7.1: Pin Configuration of SN54LS12

#### 7.5 IC Layout

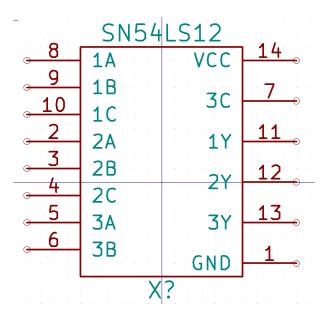

Figure 7.2: IC Layout of SN54LS12

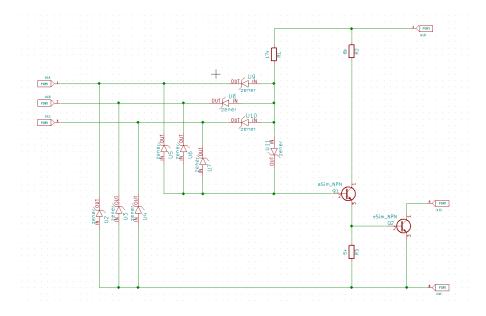

## 7.6 Subcircuit Schematic

Figure 7.3: Subcircuit Schematic of SN54LS12

## 7.7 Subcircuit Single Unit

Figure 7.4: Subcircuit Single Unit of SN54LS12

#### 7.8 Test Circuit

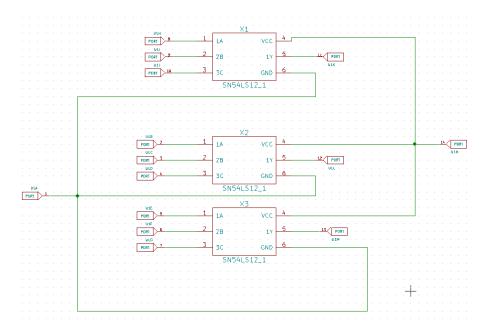

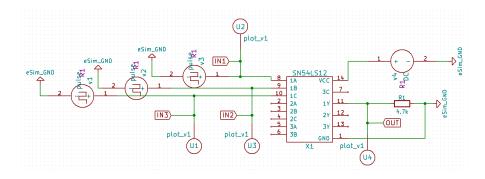

Figure 7.5: Test Circuit of SN54LS12

## 7.9 Input Plot

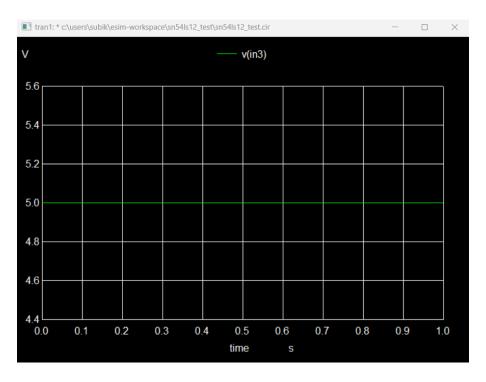

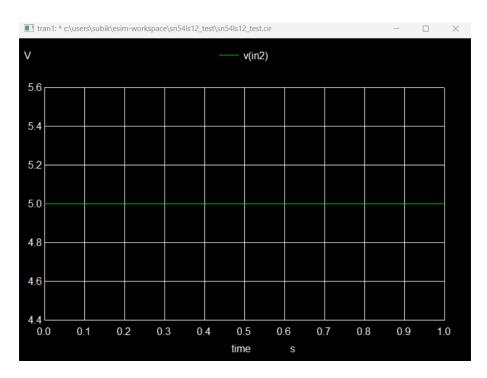

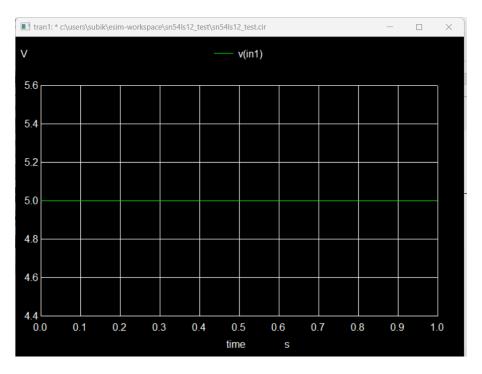

Figure 7.6: Input Plot

Figure 7.7: Input Plot

Figure 7.8: Input Plot

## 7.10 Output Plot

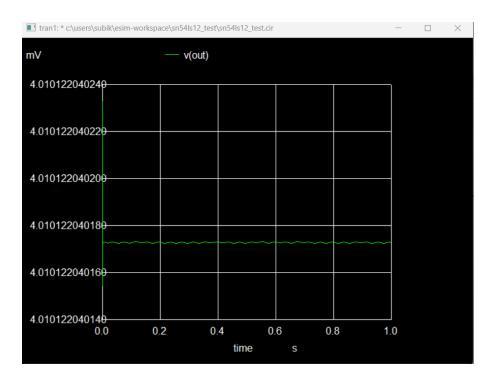

Figure 7.9: Output Plot

## SN54LS15

#### 8.1 General Description

The SN54LS15 is a dual 4-input positive-AND gate with open-collector outputs. This configuration allows each gate to sink higher currents and supports wired-AND connections (also known as wired logic). The open-collector outputs can directly drive LEDs, lamps, or other high-current loads, and also allow multiple outputs to be tied together for logic expansion without additional external logic gates. The SN54LS15 belongs to the TTL family and is designed to operate over the military temperature range from  $-55^{\circ}$ C to  $125^{\circ}$ C. Each gate provides high-speed switching with typical propagation delays around 15 ns and can sink up to 40 mA per output.

#### 8.2 Key Features

- Two 4-Input AND Gates: Combines four input signals in each gate to perform logical AND operations.

- Open-Collector Outputs: Allows higher current sinking and wired-AND logic connections.

- TTL-Compatible Inputs: Easy to interface with standard TTL logic families.

- Wide Operating Temperature Range: From -55°C to 125°C, ideal for military and industrial applications.

#### 8.3 Applications

- LED and Lamp Driving: Drives display or indicator devices requiring higher currents.

- Relay Control: Controls relays directly using open-collector outputs.

- Wired-AND Logic Implementation: Combines multiple outputs for creating custom logic functions without extra gates.

- Logic Gating and Signal Control: Used for controlling signals in complex digital systems.

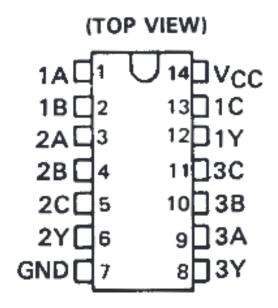

#### 8.4 Pin Configuration

Figure 8.1: Pin Configuration of SN54LS15

#### 8.5 IC Layout

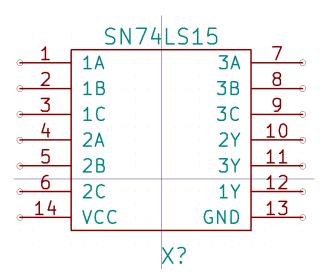

Figure 8.2: IC Layout

## 8.6 Subcircuit Single Unit Schematic

Figure 8.3: Subcircuit Single Unit of SN54LS15

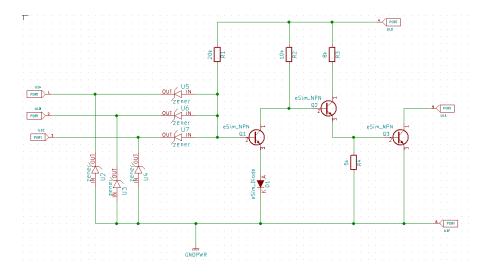

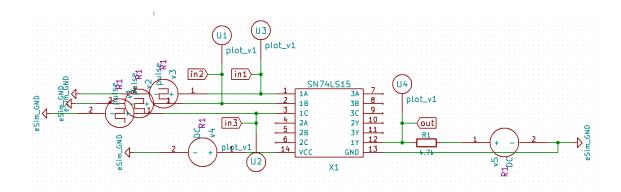

#### 8.7 Test Circuit

Figure 8.4: Enter Caption

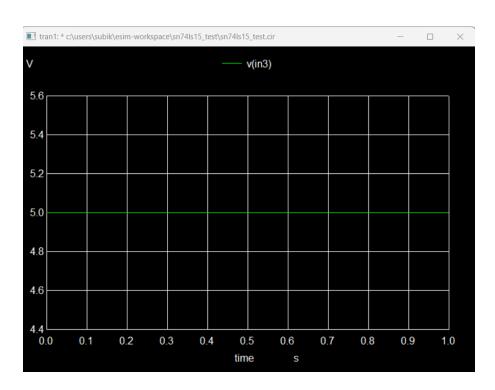

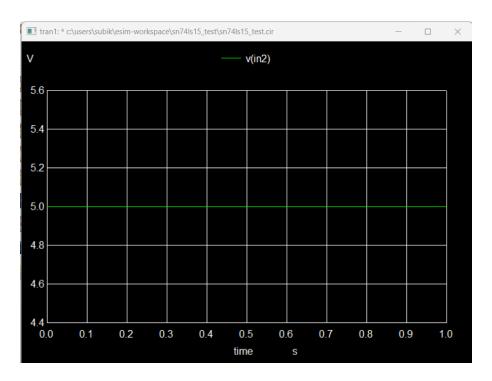

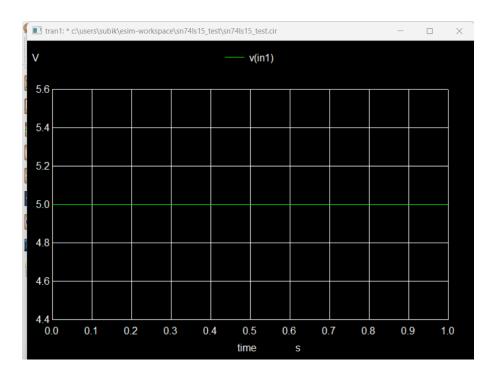

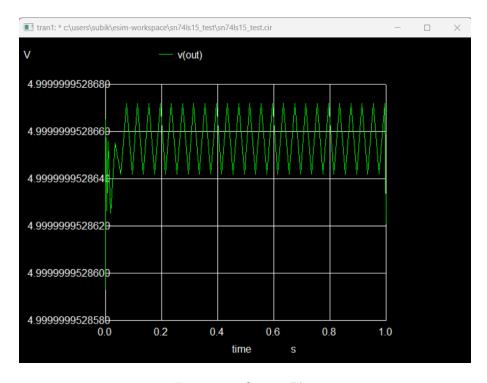

## 8.8 Input And Output Plot

Figure 8.5: Input Plot

Figure 8.6: Input Plot

Figure 8.7: Input Plot

Figure 8.8: Output Plot

# SN54LS51

## 9.1 General Description

The SN54LS51 is a dual 2-wide, 2-input AND-OR-INVERT (AOI) gate. Each gate performs the logic function  $\overline{(A \cdot B) + (C \cdot D)}$ . This device combines AND and OR logic followed by an inverting stage, enabling more complex logic functions to be implemented with fewer external gates. It belongs to the TTL logic family, ensuring high-speed switching and standard voltage compatibility. The SN54LS51 is characterized for operation over the military temperature range from  $-55^{\circ}$ C to  $125^{\circ}$ C, making it suitable for demanding industrial and defense applications. Typical propagation delay is about 10 ns, and typical power dissipation is around 33 mW per gate.

#### 9.2 Key Features

- Dual 2-Wide 2-Input AOI Gates: Provides two versatile gates that perform combined logic functions in a single package.

- TTL-Compatible Inputs and Outputs: Simplifies interfacing with other standard TTL devices.

- High-Speed Operation: Fast switching suitable for timing-critical applications.

- Wide Operating Temperature Range: From -55°C to 125°C, ideal for military and industrial environments.

#### 9.3 Applications

- Logic Function Implementation: Reduces gate count when implementing complex logic functions.

- Signal Processing and Control: Used in control logic where conditional logic decisions are needed.

- Data Routing and Multiplexing: Useful in applications requiring conditional data selection and combination.

- Timing and Synchronization Circuits: Supports logic conditions in timing-critical systems.

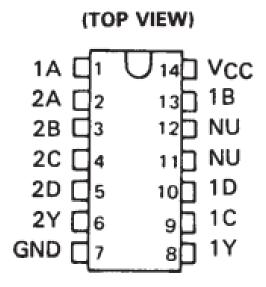

## 9.4 Pin Configuration

Figure 9.1: Pin Configuration of SN54LS51

#### 9.5 IC Layout

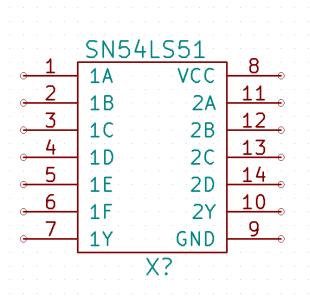

Figure 9.2: IC Layout of SN54LS51

## 9.6 Subcircuit Schematic

Figure 9.3: Subcircuit Schematic of SN54LS51

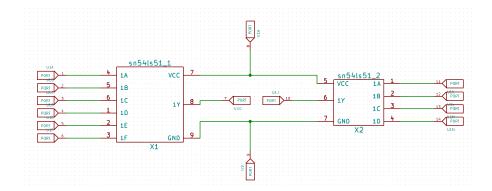

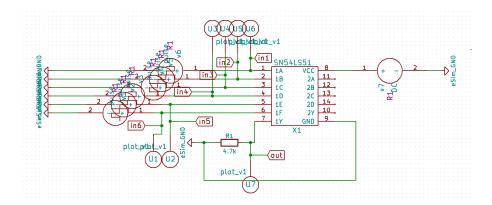

## 9.7 Test Circuit

Figure 9.4: Test Circuit of SN54LS51

# 9.8 Input And Output Plot

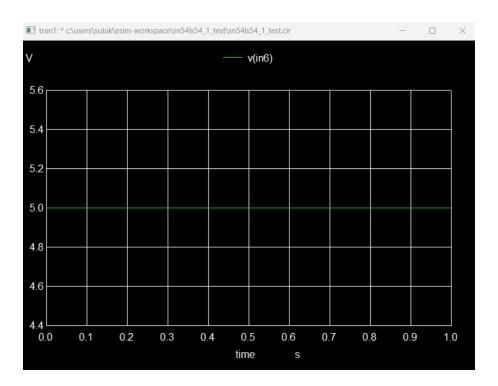

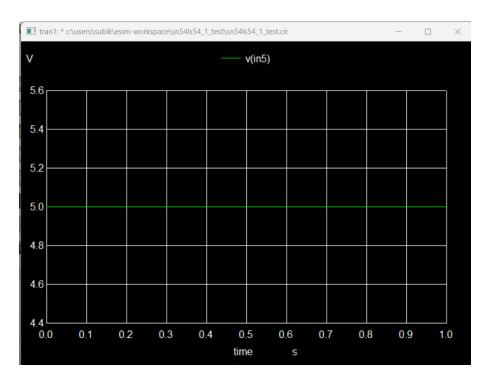

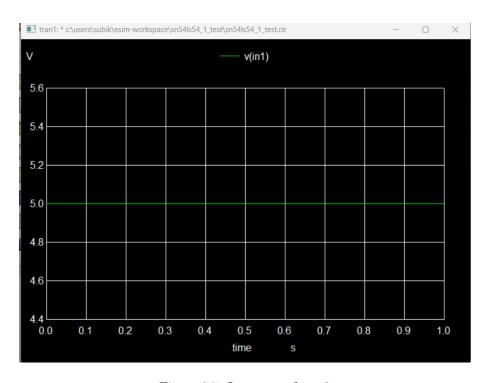

Figure 9.5: Input waveform 1

Figure 9.6: Input waveform 2

Figure 9.7: Input waveform 3

Figure 9.8: Input waveform 4

Figure 9.9: Input waveform 5

Figure 9.10: Input waveform 6

Figure 9.11: Output waveform

# **SN74LS01**

## 10.1 General Description

The SN74LS01 is a quad 2-input positive-NAND gate with open-collector outputs. Each gate performs the standard NAND logic function but uses an open-collector configuration, allowing outputs to sink higher currents and enabling wired-AND connections (wired logic). The device is a member of the TTL logic family, providing high-speed switching and standard voltage compatibility. Open-collector outputs make the SN74LS01 especially useful for driving LEDs, lamps, or interfacing with higher voltage or current circuits. Typical propagation delay is around 10 ns, and each output can sink up to 16 mA. The SN74LS01 is designed for commercial temperature ranges (0°C to 70°C).

#### 10.2 Key Features

- Four 2-Input NAND Gates: Provides versatile basic logic functions.

- Open-Collector Outputs: Allows higher current sinking and wired-AND logic configurations.

- TTL-Compatible Inputs: Ensures easy interfacing with other TTL circuits.

- Moderate Output Sink Capability: Up to 16 mA per output pin, suitable for driving small loads.

#### 10.3 Applications

- LED and Lamp Driving: Can directly drive indicator devices that require more current.

- Relay Control: Suitable for driving small relays using open-collector outputs.

- Wired-AND Logic Implementation: Supports creating custom logic functions by connecting multiple outputs together.

- General Purpose Logic Functions: Widely used for basic logic operations in digital systems.

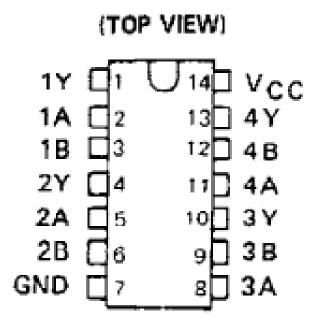

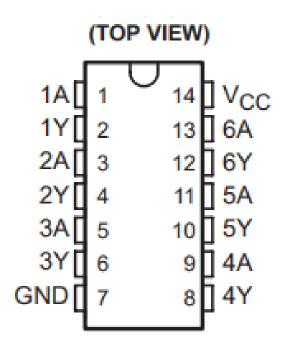

## 10.4 Pin Configuration

Figure 10.1: Pin Configuration of SN54LS01

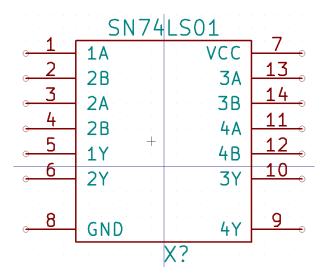

## 10.5 IC Layout

Figure 10.2: IC Layout of SN54LS01

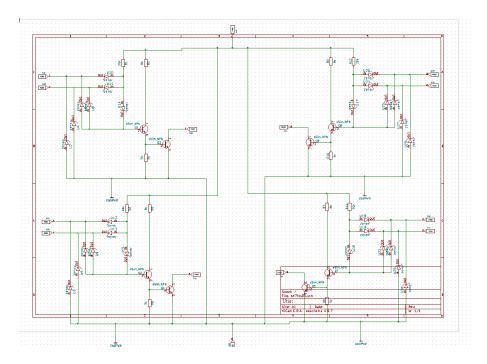

# 10.6 Subcircuit Schematic

Figure 10.3: Subcircuit Schematic of SN74LS01

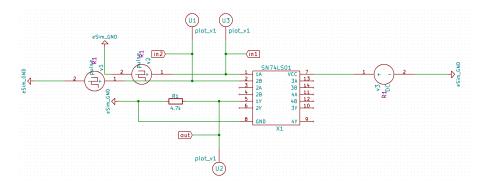

# 10.7 Test Circuit

Figure 10.4: Test Circuit of SN74LS01  $\,$

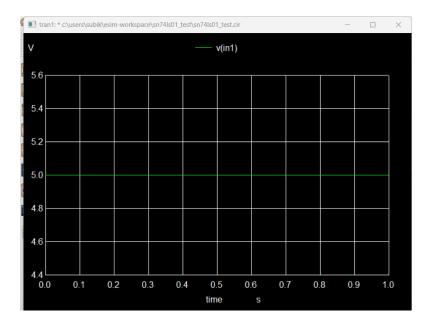

## 10.8 Input Plot 1

Figure 10.5: Input Plot 1

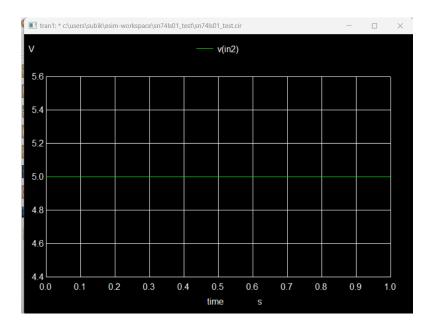

## 10.9 Input Plot 2

Figure 10.6: Input Plot 2

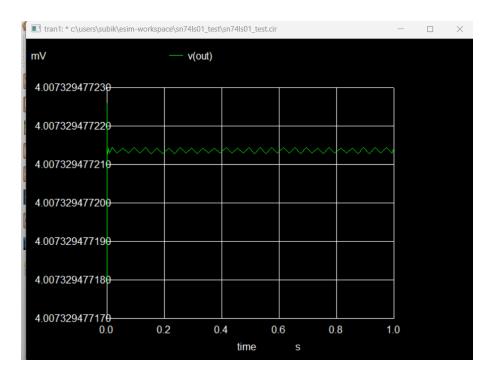

## 10.10 Output Plot

Figure 10.7: Output Plot

# SN5404

#### 11.1 General Description

The SN5404 is a hex inverter containing six independent NOT gates in a single package. Each inverter performs the logic inversion function, outputting the complement of the input signal. The SN5404 belongs to the standard 54-series TTL family, designed for high-speed operation and robust performance. It is characterized for operation over the wide military temperature range from -55°C to 125°C, making it suitable for military, aerospace, and harsh industrial environments. Typical propagation delay time is around 15 ns, and power dissipation per gate is approximately 10 mW.

#### 11.2 Key Features

- Six Independent Inverters: Provides six NOT gates in a single package for efficient logic design.

- TTL-Compatible Inputs and Outputs: Allows seamless interfacing with other standard TTL devices.

- High-Speed Switching: Supports fast logic inversion and signal processing.

- Wide Operating Temperature Range: From -55°C to 125°C, suitable for military and industrial applications.

#### 11.3 Applications

- Signal Inversion: Used for basic logic signal inversion in digital circuits.

- Oscillator and Pulse Generator Circuits: Commonly used in oscillator and waveform generation applications.

- Signal Conditioning and Buffering: Helps shape or buffer logic signals in complex systems.

- Logic Level Manipulation: Supports logic level adjustment or control in multi-level digital designs.

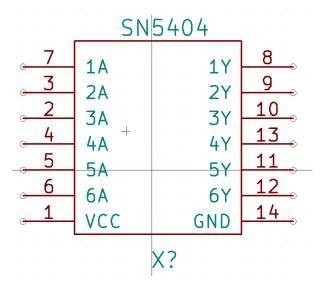

## 11.4 Pin Configuration

Figure 11.1: Pin Configuration of SN5404

#### 11.5 IC Layout

Figure 11.2: IC Layout of SN5404

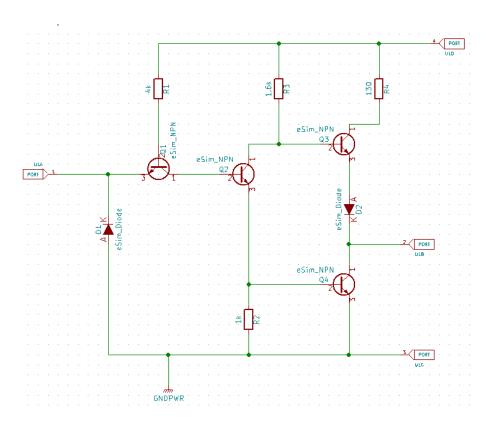

# 11.6 Single Unit Subcircuit Schematic

Figure 11.3: Subcircuit Schematic of SN5404

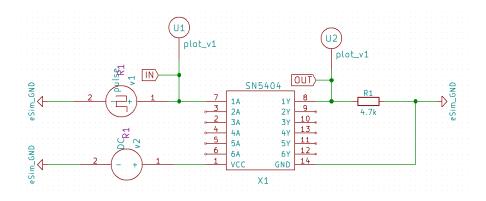

## 11.7 Test Circuit

Figure 11.4: Test Circuit of SN5404

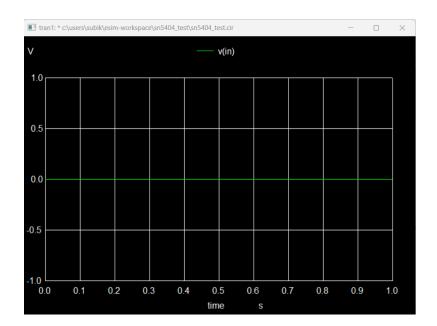

## 11.8 Input Plot

Figure 11.5: Input Plot

## 11.9 Output Plot

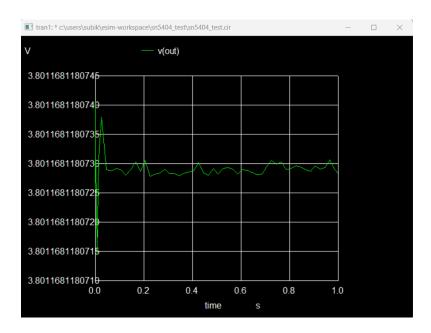

Figure 11.6: output Plot

# SN5405

## 12.1 General Description

The SN5405 is a hex inverter featuring six independent NOT gates with open-collector outputs. Each inverter performs logic inversion (NOT function), and the open-collector outputs allow these devices to sink higher currents and connect multiple outputs together in wired-AND configurations. This makes them particularly useful for driving LEDs, relays, or other loads that require higher currents, and for creating custom logic functions by tying outputs together. The SN5405 belongs to the standard 54-series TTL family, providing high-speed switching and reliable operation. It is characterized for operation over the military temperature range from -55°C to 125°C. Typical propagation delay time is around 15 ns, and each output can sink up to 30 mA.

#### 12.2 Key Features

- Six Independent Inverters: Provides six NOT gates in a single package.

- Open-Collector Outputs: Enables higher current sinking and supports wired-AND logic connections.

- TTL-Compatible Inputs: Easily interfaces with other standard TTL logic circuits.

- Wide Operating Temperature Range: From -55°C to 125°C, suitable for military and industrial applications.

#### 12.3 Applications

- LED and Lamp Driving: Used for directly driving indicator lamps and LEDs.

- Relay Control: Suitable for switching relays and higher current loads.

- Wired-AND Logic Implementation: Enables custom logic functions by connecting multiple outputs together.

- Signal Inversion and Buffering: Provides inversion and isolation in digital systems.

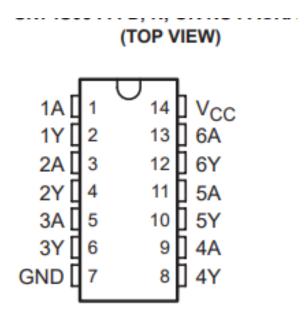

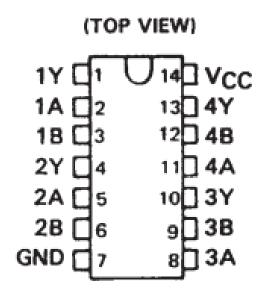

## 12.4 Pin Configuration

Figure 12.1: Pin Configuration of SN5405

## 12.5 IC Layout

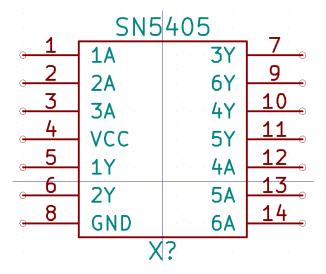

Figure 12.2: IC Layout of SN5405

## 12.6 Single Unit Subcircuit Schematic

Figure 12.3: Subcircuit Schematic of SN5405

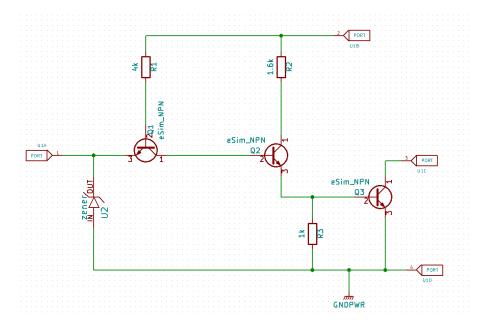

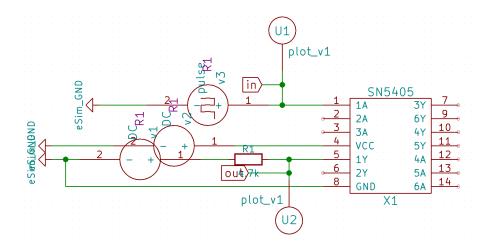

## 12.7 Test Circuit

Figure 12.4: Test Circuit of SN5405

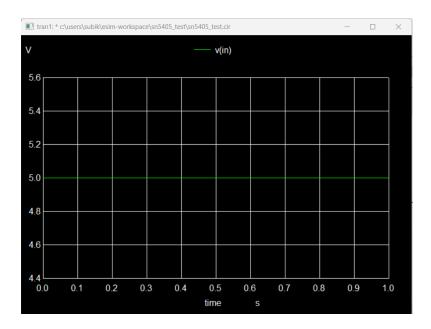

## 12.8 Input Plot

Figure 12.5: Input Plot

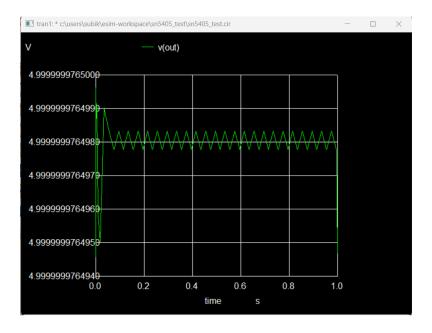

## 12.9 Output Plot

Figure 12.6: Output Plot

# SN5428

#### 13.1 General Description

The SN5428 is a dual 4-input positive-NOR gate. Each gate performs the logical NOR operation on four inputs, outputting a high logic level only when all inputs are low. By combining multiple signals, the SN5428 can implement complex logic functions in digital systems. It belongs to the standard 54-series TTL family, ensuring high-speed switching and reliable operation. The SN5428 is characterized for operation over the military temperature range from  $-55^{\circ}$ C to  $125^{\circ}$ C, making it ideal for defense, aerospace, and industrial applications. Typical propagation delay time is around 10 ns, and typical power dissipation is about 33 mW per gate.

#### 13.2 Key Features

- Two 4-Input NOR Gates: Provides two versatile logic gates for combining up to four signals each.

- TTL-Compatible Inputs and Outputs: Easily interfaces with other standard TTL logic circuits.

- High-Speed Operation: Suitable for timing-critical and high-speed logic applications.

- Wide Operating Temperature Range: From -55°C to 125°C, ideal for military and harsh industrial environments.

## 13.3 Applications

- Logic Function Implementation: Used to simplify complex logic conditions in digital circuits.

- Signal Gating and Control: Controls the flow of signals based on multiple logic conditions.

- Pulse and Timing Circuits: Useful in generating or shaping timing signals in digital systems.

- Data Selection and Combination: Combines multiple data lines based on NOR logic requirements.

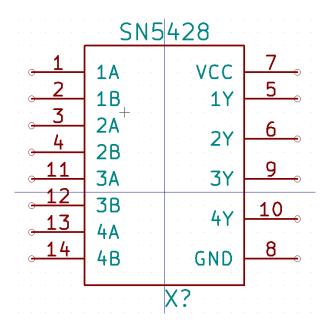

## 13.4 Pin Configuration

Figure 13.1: Pin Configuration of SN5428

## 13.5 IC Layout

Figure 13.2: IC Layout of SN5428

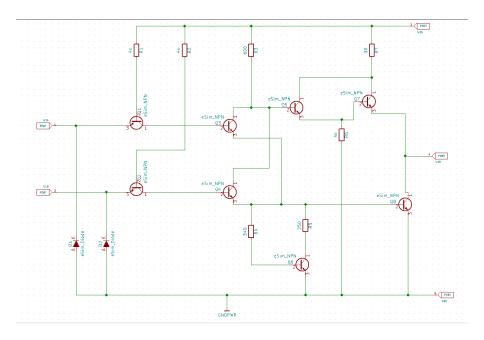

# 13.6 Single Unit Subcircuit Schematic

Figure 13.3: Single Unit Subcircuit Schematic of  ${\rm SN}5428$

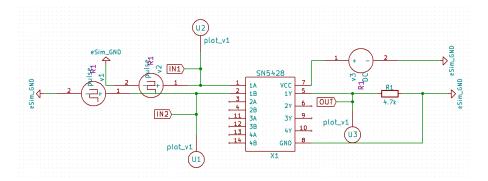

## 13.7 Test Circuit

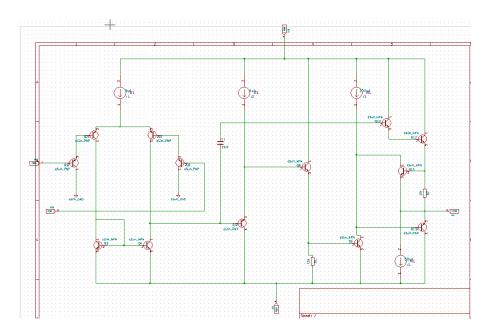

Figure 13.4: Test Circuit of SN5428

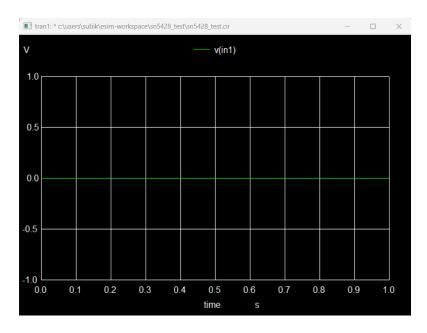

## 13.8 Input Plot 1

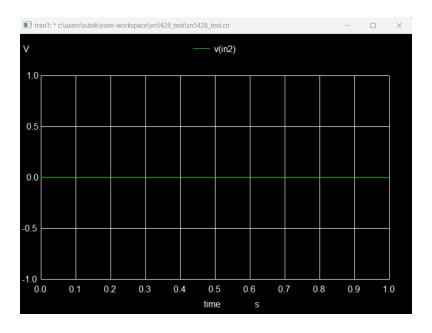

Figure 13.5: Input Plot 1

## 13.9 Input Plot 2

Figure 13.6: Input Plot 2

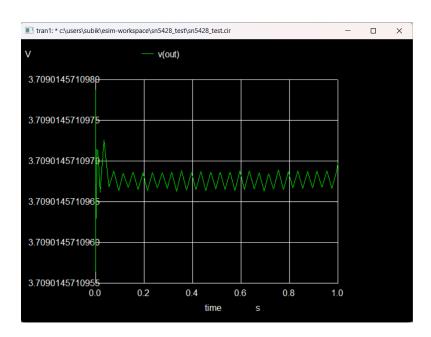

## 13.10 Output Plot

Figure 13.7: Output Plot

# Failed Circuits

#### 14.1 Overview

In this section, we discuss circuits that did not perform as expected during testing. Understanding the reasons for these failures helps in diagnosing issues and improving circuit design. Each failed circuit is analyzed to identify the potential causes of failure and to suggest corrective measures.

#### 14.2 TS321

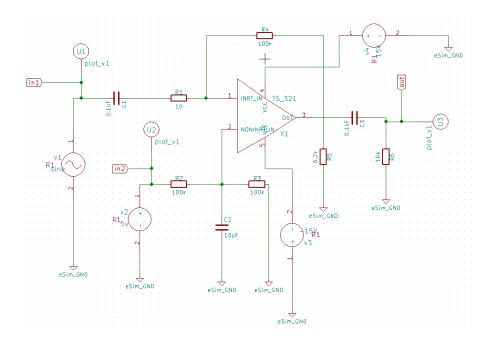

Figure 14.1: Subcircuit of TS321

#### **Issue Description**

While simulating the TS321 operational amplifier in eSim, I encountered issues such as unexpected output behavior and failure to achieve proper voltage levels. These problems were primarily due to limitations in the available simulation model and potential internal characteristics not fully supported by eSim's op-amp library. The simulation would either not converge or produce distorted output waveforms that did not match expected datasheet performance. Despite verifying all connections and using standard biasing and load configurations, the issue persisted. As a result, the TS321 simulation could not be completed successfully, and the IC was documented as a failed circuit contribution in this project.

# 14.3 Test Circuit

Figure 14.2: Test Circuit of TS321

# Conclusion and Future Scope

The project achieved its objective of developing a wide range of subcircuits for both Analog and Digital Integrated Circuits, with each IC model meticulously crafted based on the specifications provided in their official datasheets. Through rigorous testing and verification using corresponding test circuits, these IC models were validated for accuracy and functionality. The components developed under this fellowship encompass fundamental circuit elements such as Operational Amplifiers (Op-Amps), Voltage Regulators, Precision Rectifiers, Schmitt Triggers, Differential Amplifiers, Instrumentation Amplifiers, Comparators, Multiplexers, De-Multiplexers, and various Logic Gate ICs. These models are now ready for integration into the eSim subcircuit library, providing a robust resource for developers, students, and researchers. The inclusion of these models in the eSim library will significantly enhance the tool's capabilities, enabling users to easily incorporate these fundamental ICs into their own projects and circuit designs. Looking ahead, this project sets the foundation for the continued expansion of eSim's device model library. We anticipate that more such ready-to-use IC models will be developed, broadening the scope of available components and further empowering the eSim community. This ongoing development will not only aid in academic and research endeavors but also contribute to the growing ecosystem of open-source electronic design automation (EDA) tools.

# Circuits Contribution

This chapter lists all the Integrated Circuits (ICs) contributed during the fellowship. Each IC has been carefully modeled and tested, and is now part of the eSim library. The contributions include both analog and digital ICs, covering a wide range of functionalities.

#### 16.1 Subikeesh M List of ICs

- 1. SN54LS06 A hex inverter buffer IC with open-collector outputs and military-grade temperature range.

- 2. SN54LS10 A triple 3-input NAND gate IC designed for complex logic implementations.

- 3. SN54LS11 A triple 3-input AND gate IC supporting high-speed logic operations.

- 4. SN54LS12 A dual 4-input NAND gate IC with open-collector outputs for driving higher current loads.

- 5. SN54LS15 A dual 4-input AND gate IC with open-collector outputs for wired logic and high-current loads.

- 6. SN54LS51 A dual 2-wide 2-input AND-OR-INVERT (AOI) gate IC for compact complex logic functions.

- 7. SN74LS01 A quad 2-input NAND gate IC with open-collector outputs.

- 8. SN5404 A hex inverter IC designed for high-speed logic inversion and signal conditioning.

- 9. SN5405 A hex inverter IC with open-collector outputs for higher current driving and wired-AND logic.

- 10. SN5428 A dual 4-input NOR gate IC used in complex logic gating and signal control.

# **Bibliography**

- [1] FOSSEE Official Website. https://fossee.in

- [2] eSim Official Website. https://esim.fossee.in/

- [3] Texas Instruments, SN54LS06 Datasheet. https://www.ti.com/lit/ds/symlink/sn54ls06.pdf

- [4] Texas Instruments, SN54LS10 Datasheet. https://www.ti.com/lit/ds/symlink/sn54ls10.pdf

- [5] Texas Instruments, SN54LS11 Datasheet. https://www.ti.com/lit/ds/symlink/sn54ls11.pdf

- [6] Texas Instruments, SN54LS12 Datasheet. https://www.alldatasheet.com/datasheet-pdf/ view/27356/TI/SN54LS12.html

- [7] Texas Instruments, SN54LS15 Datasheet. https://www.alldatasheet.com/datasheet-pdf/pdf/27983/TI/SN54LS15.html

- [8] Texas Instruments, SN54LS51 Datasheet. https://www.ti.com/lit/ds/symlink/sn54ls51.pdf

- [9] SN74LS01 Datasheet. https://www.unicornelectronics.com/ftp/Data%20Sheets/7401.pdf

- [10] Texas Instruments, SN5404 Datasheet. https://www.ti.com/lit/ds/symlink/sn5404.pdf

- [11] Texas Instruments, SN5405 Datasheet. https://www.ti.com/lit/ds/symlink/sn7405.pdf

- [12] Texas Instruments, SN5428 Datasheet. https://www.ti.com/lit/ds/symlink/sn5428.pdf