## Winter Internship Report On Integrated Circuit Design using Subcircuit Feature of eSim

$\begin{array}{c} {}_{\rm Submitted \ by} \\ {\bf Sagarikaa} \ R \ K \end{array}$

$\begin{array}{c} {\rm Under \ the \ guidance \ of} \\ {\rm Prof. \ Kannan \ M. \ Moudgalya} \\ {\rm Chemical \ Engineering \ Department} \\ {\rm IIT \ Bombay} \end{array}$

February 13, 2025

# Acknowledgment

We take this occasion to offer our heartfelt gratitude to the FOSSEE, IIT Bombay Team for offering us this wonderful opportunity to work on the design and integration of multiple sub-circuits in eSim. Working on eSim has provided us with invaluable insights into various open-source EDA tools for circuit simulation and their applications in the practical world.

We extend our sincere regards to Prof. Kannan M. Moudgalya for his valuable guidance and motivation throughout this fellowship program. We would like to express our heartfelt appreciation to the entire FOSSEE team, including our mentors Mr. Sumanto Kar, Ms. Usha Vishwanathan and Ms. Vineeta Ghavri, for constantly guiding and mentoring us throughout the duration of our internship.

It is with their support that we have been able to fulfill our project demands successfully. Whenever faced with an issue, our mentors were always accessible to help us assess and debug them. Our learnings from them have been invaluable and shall be of paramount importance to us in the future.

Overall, it was a delightful experience interning at FOSSEE and contributing to its growth. I take away some great insights and knowledge from it. As enthusiastic beginners in the semiconductor industry, this internship is a milestone for us in our pursuit of a successful career.

# Contents

| 1 | Introduction                     | 4    |

|---|----------------------------------|------|

|   | 1.1 FOSSEE                       | . 4  |

|   | 1.2 eSim                         | . 4  |

|   | 1.3 NgSpice                      | . 4  |

|   | 1.4 Makerchip                    |      |

| 2 | Features of eSim                 | 6    |

| 3 | Problem Statement                | 7    |

| 0 | 3.1 Approach                     | •    |

|   | 5.1 Approach                     | . 1  |

| 4 | SN5410                           | 9    |

|   | 4.1 General Description          | . 9  |

|   | 4.2 Key Features                 | . 9  |

|   | 4.3 Applications                 | . 9  |

|   | 4.4 Pin Configuration            | . 9  |

|   | 4.5 IC Layout                    | . 10 |

|   | 4.6 Subcircuit Schematic         |      |

|   | 4.7 Test Circuit                 | . 11 |

|   | 4.8 Output Plot HIGH             |      |

|   | 4.9 Output Plot LOW              |      |

| - |                                  | 10   |

| 5 | LM431                            | 13   |

|   | 5.1 General Description          |      |

|   | 5.2 Key Features                 |      |

|   | 5.3 Applications                 |      |

|   | 5.4 Pin Configuration            |      |

|   | 5.5 IC Layout                    |      |

|   | 5.6 Subcircuit Schematic Diagram |      |

|   | 5.7 Test Circuit                 |      |

|   | 5.8 Input Plot                   |      |

|   | 5.9 Output Plot                  | . 16 |

| 6 | SN7420                           | 17   |

| U | 6.1 General Description          |      |

|   | ÷                                |      |

|   | V                                |      |

|   | 6.3 Applications                 |      |

|   | 6.4 Pin Configuration            |      |

|   | 6.5 IC Layout                    |      |

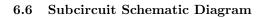

|   | 6.6 Subcircuit Schematic Diagram |      |

|   | 6.7 Test Circuit                 |      |

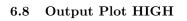

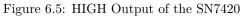

|   | 6.8 Output Plot HIGH             |      |

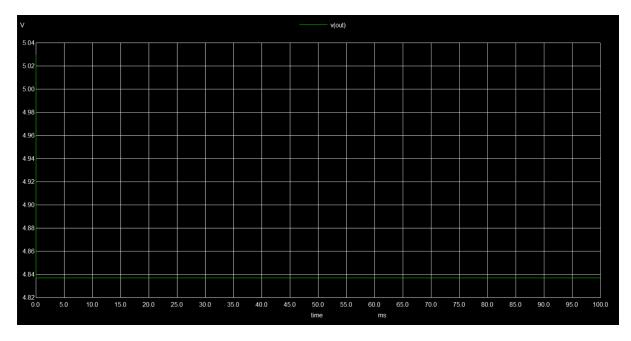

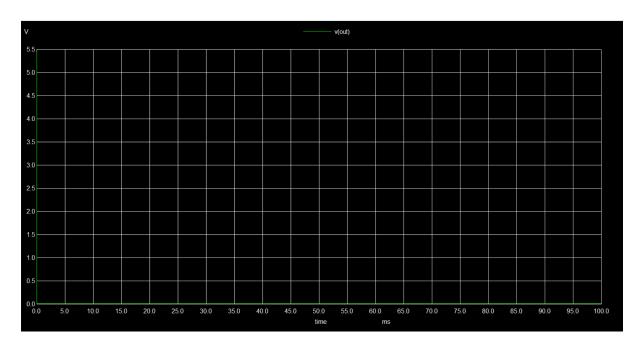

|   | 6.9 Output Plot LOW              | . 20 |

| <b>7</b> | L60  | 1                            | <b>21</b>  |

|----------|------|------------------------------|------------|

|          | 7.1  | General Description          | 21         |

|          | 7.2  | Key Features                 | 21         |

|          | 7.3  | Applications                 | 21         |

|          | 7.4  | Pin Configuration            | 21         |

|          | 7.5  | IC Layout                    | 22         |

|          | 7.6  | Subcircuit Schematic         | 22         |

|          | 7.7  | Test Circuit                 | 23         |

|          | 7.8  | Input Plot                   | 23         |

|          | 7.9  | Output Plot                  | 24         |

| 8        | SN5  | 54LS30                       | 25         |

|          | 8.1  | General Description          | 25         |

|          | 8.2  | Key Features                 | 25         |

|          | 8.3  | Applications                 | 25         |

|          | 8.4  | Pin Configuration            | 25         |

|          | 8.5  | IC Layout                    | 26         |

|          | 8.6  | Subcircuit Schematic Diagram | 26         |

|          | 8.7  | Test Circuit                 | 27         |

|          | 8.8  | Output Plot HIGH             | 27         |

|          | 8.9  | Output Plot LOW              | 28         |

| 9        | Fail | ed Circuits                  | 29         |

|          | 9.1  | Overview                     | 29         |

|          | 9.2  | LP2954                       | 29         |

|          | 9.3  | OP470                        | 31         |

|          | 9.4  | TL783                        | 33         |

| 10       | Con  | clusion and Future Scope     | <b>35</b>  |

| 11       | Circ | cuits Contribution           | 36         |

| 11       |      | Sagarikaa R K List of ICs    | <b>3</b> 6 |

# Introduction

## 1.1 FOSSEE

FOSSEE, which stands for Free/Libre and Open Source Software for Education, is an organization based at IIT Bombay. It is a remarkable initiative aimed at promoting the use of open-source software in education and research. It was established with the mission to reduce dependency on proprietary software and to encourage the adoption of open-source alternatives. FOSSEE offers a wide range of tools and resources that cater to various academic and professional needs.

It provides comprehensive documentation, tutorials, workshops, and hands-on training sessions to empower students, educators, and professionals to leverage open-source software for their projects and coursework. The organization's commitment to fostering a collaborative and inclusive environment has significantly contributed to the democratization of technology and has opened up new avenues for innovation and learning

#### **1.2** eSim

eSim, created by the FOSSEE project at IIT Bombay, is a versatile open-source software tool for circuit design and simulation. It combines various open-source software packages into one cohesive platform, making it easier to design, simulate, and analyze electronic circuits. This tool is particularly useful for students, educators, and professionals who need an affordable and accessible alternative to proprietary software.

eSim offers features for schematic creation, circuit simulation, and PCB design, and includes an extensive library of components. The Subcircuit feature is a significant enhancement, enabling users to design complex circuits by integrating simpler subcircuits. Through eSim, FOSSEE promotes the use of open-source solutions in engineering education and professional fields, encouraging innovation and collaboration.

## 1.3 NgSpice

NgSpice is an open-source SPICE simulator for electric and electronic circuits. It can simulate various circuit elements, including JFETs, bipolar and MOS transistors, passive elements (R, L, C), diodes and other devices, all interconnected in a netlist.

Digital circuits are also simulated, ranging from single gates to complex circuits, including combinations of analog, digital, and mixed-signal circuits. NgSpice offers a wealth of device models for active, passive, analog, and digital elements. Users input their circuits as netlists, and the output is one or more graphs of currents, voltages, and other electrical quantities, or saved in a data file

#### 1.4 Makerchip

Makerchip is a platform that offers convenient and accessible tools for digital circuit design. It provides both browser-based and desktop-based environments for coding, compiling, simulating, and debugging Verilog designs. Makerchip supports a combination of open-source and proprietary tools, ensuring a comprehensive range of capabilities.

Users can simulate Verilog/SystemVerilog/Transaction-Level Verilog code in Makerchip. eSim is interfaced with Makerchip using a Python-based application called Makerchip-App, which launches the Makerchip IDE. Makerchip aims to make circuit design easy and enjoyable for users of all skill levels. The platform provides a userfriendly interface, intuitive workflows, and a range of helpful features that simplify the design process and enhance the overall user experience.

The main drawback of these open-source tools is that they are not comprehensive. While some are capable of PCB design (e.g., KiCad), others focus on simulations (e.g., gEDA). To the best of our knowledge, there is no open-source software that combines circuit design, simulation, and layout design in one platform. eSim addresses this gap by integrating all these capabilities.

# Features of eSim

The objective behind the development of eSim is to provide an open-source EDA solution for electronics and electrical engineers. The software is capable of performing schematic creation, PCB design, and circuit simulation (analog, digital, and mixedsignal). It also provides facilities to create new models and components. Thus, eSim offers the following features:

1. Schematic Creation: eSim provides an easy-to-use graphical interface for drawing circuit schematics, making it accessible for users of all levels. Users can drag and drop components from the library onto the schematic, simplifying the design process. Comprehensive editing tools allow for easy modification of schematics, including moving, rotating, and labeling components.

**2.** Circuit Simulation: eSim supports SPICE (Simulation Program with Integrated Circuit Emphasis), a standard for simulating analog and digital circuits. Users can perform various types of analysis such as transient, AC, and DC, providing insights into circuit behavior over time and frequency. An integrated waveform viewer helps visualize simulation results, aiding in the analysis and debugging of circuit designs.

**3. PCB Design:** The PCB layout editor allows users to place components and route traces with precision. eSim includes DRC (Design Rule Check) capabilities to ensure that the PCB design adheres to manufacturing constraints and electrical rules. Users can generate Gerber files, which are standard for PCB fabrication, directly from their designs.

4. Subcircuit Feature: This feature enables users to create complex circuits by integrating smaller, simpler subcircuits, promoting modular and hierarchical design approaches. Subcircuits can be reused in different projects, saving time and effort in redesigning common circuit elements.

5. Open Source Integration: eSim integrates several open-source tools like KiCad, NgSpice, and GHDL, providing a comprehensive suite for electronic design automation. Being open-source, eSim is free to use, making advanced circuit design tools accessible without the need for expensive licenses.

## **Problem Statement**

To design and develop various analog and digital integrated circuit models in the form of sub-circuits using device model files already present in the eSim library. These IC models should be useful for future circuit design purposes by developers and users once they are successfully integrated into the eSim subcircuit library.

## 3.1 Approach

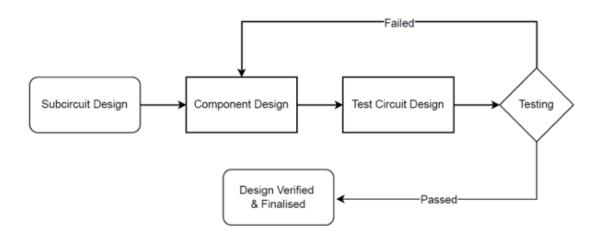

Figure 3.1: Flowchart of IC Design Approach Followed

Our approach to implementing the problem statement involved a systematic process, leveraging datasheets from leading Integrated Circuit (IC) manufacturers such as Texas Instruments, Analog Devices, and NXP Semiconductors. We focused on selecting ICs with diverse functionalities, including precision amplifiers, comparators, encoders, and audio amplifiers. The process is outlined in the following steps:

1. Analyzing Datasheets: The first step involved an in-depth review of datasheets for various analog and digital ICs. We aimed to identify circuits suitable for implementation in eSim that were not already present in the eSim library. This process included scrutinizing the detailed schematics of each IC, evaluating component values, and understanding truth tables. The goal was to select ICs that offered unique functionalities or enhancements not yet covered.

2. Subcircuit Creation: After selecting appropriate ICs, we proceeded to model these as sub-circuits within eSim. We utilized the model files available in the eSim device model library and ensured that our designs adhered strictly to the specifications outlined in the official datasheets. This phase also involved

creating accurate symbol and pin diagrams for each IC, in accordance with the packaging and pin descriptions provided in the datasheets. This step was crucial for ensuring the fidelity of the subcircuit models.

**3.** Test Circuit Design: With the sub-circuits created, we then designed and built test circuits based on the datasheets. This step was essential for verifying the functionality of each sub-circuit. We developed a series of test cases and constructed corresponding test circuits to evaluate the performance and accuracy of the implemented IC models.

4. Schematic Testing: Following the construction of test circuits, we conducted simulations to analyze the outputs. This involved generating waveforms and plots to assess the behavior of the circuits. We employed KiCad for converting designs to NgSpice netlists and utilized eSim's simulation features to perform comprehensive testing.

If the simulated outputs deviated from expected results, it signaled potential errors in the schematic. In such instances, we revisited the design phase to identify and correct discrepancies. The iterative process of debugging and re-testing continued until the test cases produced satisfactory results. Once the IC models met the desired performance criteria, they were deemed successful, marking the completion of the design process

# **SN5410**

#### 4.1 General Description

The SN5410 is a triple 3-input positive NAND gate, meaning it contains three independent NAND gates, each with three inputs. The SN5410 is a TTL logic IC that contains three independent NAND gates, each with three inputs. It follows positive logic, meaning the output is LOW only when all inputs are HIGH. It operates using 5V TTL logic levels and is part of the SN54 series, which is designed for military and aerospace applications due to its extended temperature range (-55°C to 125°C).

The SN5410 is functionally identical to the SN7410, which is used in commercial applications.

#### 4.2 Key Features

- Standard TTL voltage levels : operates around 4.75V to 5.25V.

- Military-grade temperature range :-55°C to 125°C.

- Low Power Consumption: Optimized for efficient operation in digital systems.

- Fast Switching Times : Short propagation delays, suitable for high-speed applications.

#### 4.3 Applications

- Data Processing Control Circuits : Found in CPUs, ALUs, and other logic-based processors.

- Signal Processing : Used in control logic and waveform shaping applications.

- Clock and Timing Circuits: Used in pulse generation and logic timing applications.

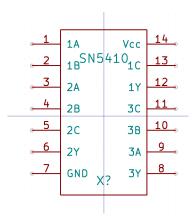

### 4.4 Pin Configuration

| -   |            |      |             |  |  |  |

|-----|------------|------|-------------|--|--|--|

|     | (TOP VIEW) |      |             |  |  |  |

| 1A  | đ٢         | U14  | Þ vcc       |  |  |  |

| 1B  |            | 13   | <b>□</b> 1C |  |  |  |

| 2A  | <b>q</b> 3 | 12   | Þ 1Y        |  |  |  |

| 2B  | Q₄         | . 11 | □зс         |  |  |  |

| 2C  | ٩          | 5 10 | 🛛 ЗВ        |  |  |  |

| 2Y  | ٩e         | 5 9  | <b>□</b> 3A |  |  |  |

| GND | Q2         | , 8  | р зү        |  |  |  |

Figure 4.1: Pin Configuration of the SN5410

## 4.5 IC Layout

Figure 4.2: IC Layout of the SN5410

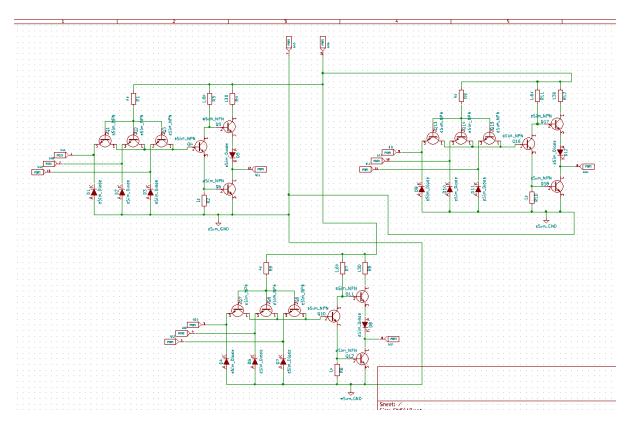

## 4.6 Subcircuit Schematic

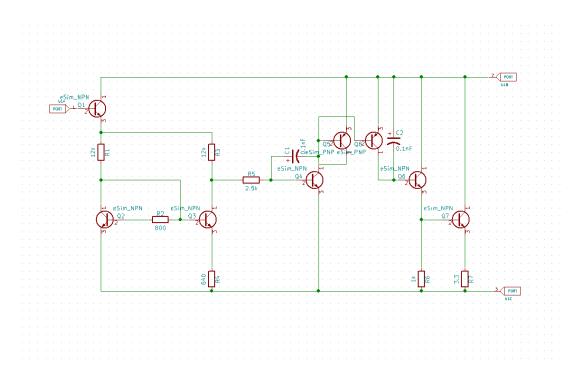

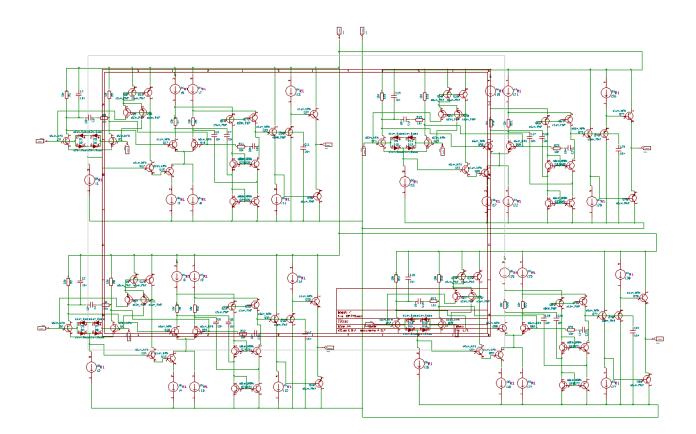

Figure 4.3: Subcircuit Schematic of the SN5410

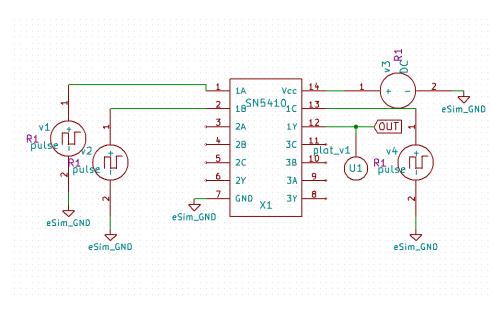

## 4.7 Test Circuit

Figure 4.4: Test Circuit of the SN5410

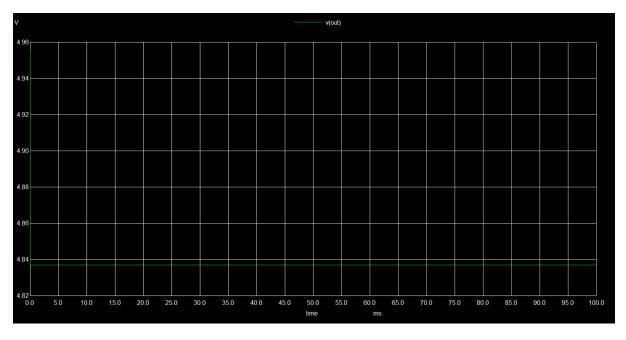

## 4.8 Output Plot HIGH

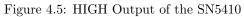

## 4.9 Output Plot LOW

# LM431

#### 5.1 General Description

The LM431 is an adjustable shunt voltage regulator that functions similarly to a Zener diode but with greater precision and control. It operates as a programmable voltage reference with an output voltage that can be adjusted from 2.5V to 36V using an external resistor divider. The IC is widely used in power management circuits, voltage regulation, and voltage monitoring applications.

## 5.2 Key Features

- Adjustable Output Voltage: 2.5V to 36V

- High Accuracy: ±1

- Low Temperature Coefficient: Ensures stable operation across different temperatures.

- Low Output Impedance:Improves performance in regulation applications.

- Wide Operating Current Range: 1mA to 100mA.

- Fast Response Time: Suitable for dynamic voltage regulation.

#### 5.3 Applications

- Voltage Regulation: Used as a precision voltage reference in power supplies.

- Switching Power Supplies: Provides stable reference voltage for SMPS circuits.

- Overvoltage and Undervoltage Protection: Helps in monitoring and controlling voltage levels.

- Adjustable Power Supplies: Allows fine-tuning of output voltage in electronic projects.

- 5.4 Pin Configuration

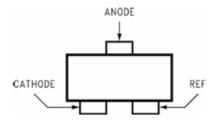

Figure 5.1: Pin Configuration of the LM431

## 5.5 IC Layout

Figure 5.2: IC Layout of LM431

## 5.6 Subcircuit Schematic Diagram

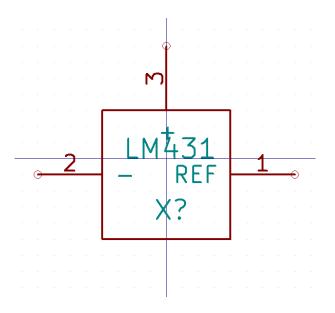

Figure 5.3: Subcircuit Schematic Diagram of the LM431

## 5.7 Test Circuit

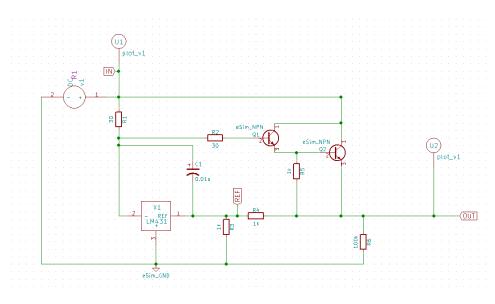

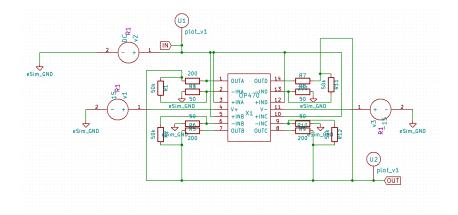

Figure 5.4: Test Circuit of the LM431

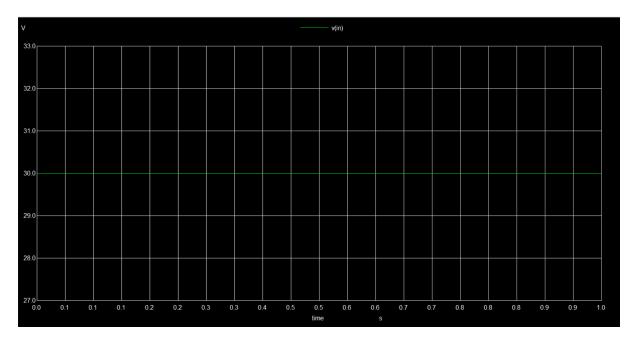

## 5.8 Input Plot

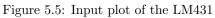

## 5.9 Output Plot

# SN7420

#### 6.1 General Description

The SN7420 is a dual 4-input positive NAND gate IC from the 74xx series of TTL logic gates. It contains two independent NAND gates, each with four inputs. The output of each gate is LOW only when all four inputs are HIGH; otherwise, the output remains HIGH. It is widely used in digital logic applications requiring high-input NAND operations, including control circuits, timing circuits, and address decoding.

## 6.2 Key Features

- Dual 4-Input NAND Gates: Two independent NAND gates with four inputs each..

- TTL-Compatible: Standard TTL voltage and logic levels.

- Positive Logic Operation: Outputs LOW only when all four inputs are HIGH.

- Operating Voltage Range: 4.75V to 5.25V (Standard 5V TTL logic)

- High Fan-Out Capability: Can drive multiple logic inputs

#### 6.3 Applications

- Address Decoding: Used in memory and microprocessor-based systems.

- Logic Control Circuits: Common in industrial and automation systems.

- Security and Alarm Systems: Used in decision-making logic circuits.

- Data Processing Circuits: Helps in logic signal filtering and manipulation.

## 6.4 Pin Configuration

| 1 <b>A</b> | d,         | U14 VCC        |

|------------|------------|----------------|

| 1B         |            | 13 2D          |

| NC         | ₫3         | 120 2C         |

| 1C         | ₫₄         | INC LIFE       |

| 1D         | đ۶         | 10 <b>] 2B</b> |

| 1Y         | <b>₫</b> 6 | 9] 2A          |

| GND        | d۶.        | 8 🗍 2 Y        |

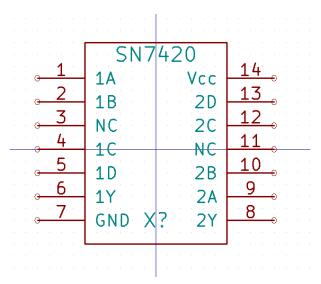

Figure 6.1: Pin Configuration of SN7420

Figure 6.2: IC Layout of the SN7420

Figure 6.3: Subcircuit Schematic of the SN7420

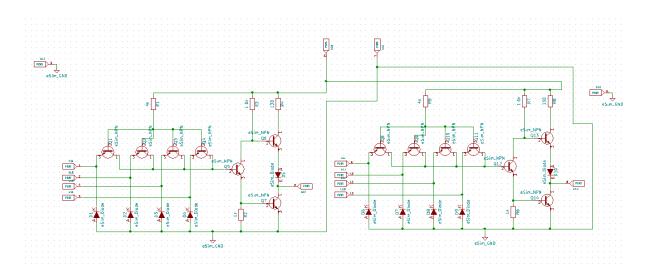

## 6.7 Test Circuit

Figure 6.4: Test Circuit of the SN7420

## 6.9 Output Plot LOW

Figure 6.6: LOW Output of the SN7420  $\,$

# L601

## 7.1 General Description

The L601 is a Darlington transistor array, designed for high-current, high-voltage applications. It typically consists of multiple Darlington transistor pairs with common emitter and open-collector outputs, enabling it to drive inductive loads such as relays, motors, solenoids, and LED displays. This IC is often used in interfacing low-power logic circuits with high-power loads.

## 7.2 Key Features

- Multiple Darlington Transistor Pairs: Provides high current gain.

- Open-Collector Outputs:Ideal for driving relays, solenoids, and stepper motors.

- TTL and CMOS Compatible Inputs: Works with microcontrollers and logic circuits.

## 7.3 Applications

- Relay and Solenoid Driving: Controls electromechanical devices.

- Motor Control: Drives stepper and DC motors in automation systems.

- LED and Display Drivers: Powers LED matrix displays and seven-segment displays.

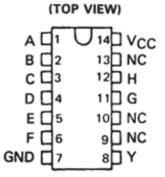

- 7.4 Pin Configuration

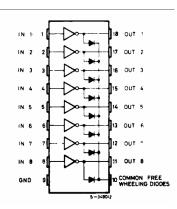

Figure 7.1: Pin Configuration of the L601

## 7.5 IC Layout

| <u> </u>                              | IN1  |    |             | OUT1 | 18 。 |

|---------------------------------------|------|----|-------------|------|------|

| <u>, 2</u>                            | IN2  |    |             | OUT2 | 17_  |

| <u>, 3</u>                            | IN 3 |    |             | OUT3 | 16   |

| • 4                                   | IN 4 | L6 | 01          | OUT4 | 15_  |

| <u>, 5 </u>                           | IN5  |    | 2<br>2<br>2 | OUT5 | 14 0 |

| <u> </u>                              | IN6  |    | •           | OUT6 | 13   |

| <del>.</del> 7                        | IN7  |    |             | OUT7 | 12 。 |

| <u>8</u>                              | IN8  |    |             | OUT8 | 11   |

| · · · · · · · · · · · · · · · · · · · | GND  |    |             | СОМ  | 10   |

|                                       |      |    | <br>        |      | I    |

|                                       |      |    |             |      |      |

Figure 7.2: IC Layout of the L601

## 7.6 Subcircuit Schematic

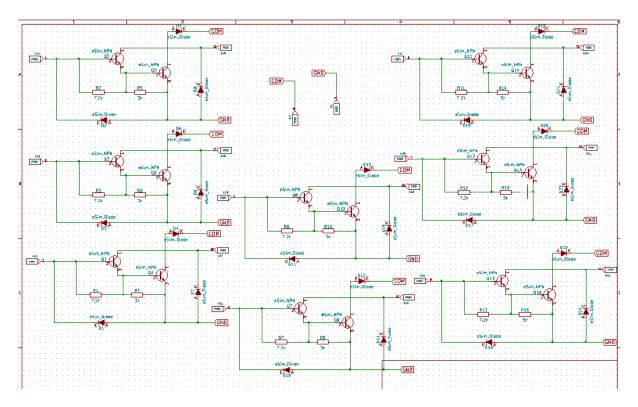

Figure 7.3: Subcircuit Schematic of the L601

## 7.7 Test Circuit

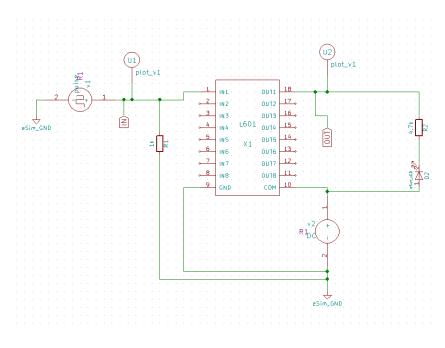

Figure 7.4: Test Circuit of the L601

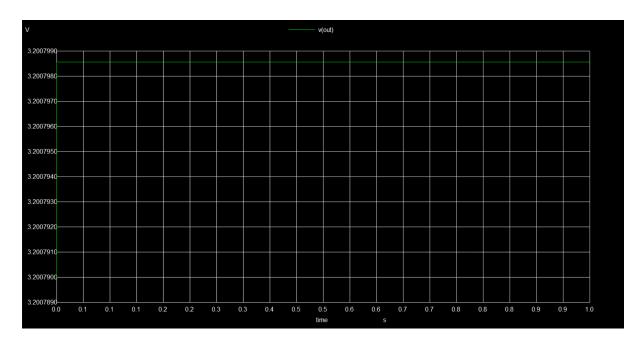

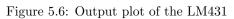

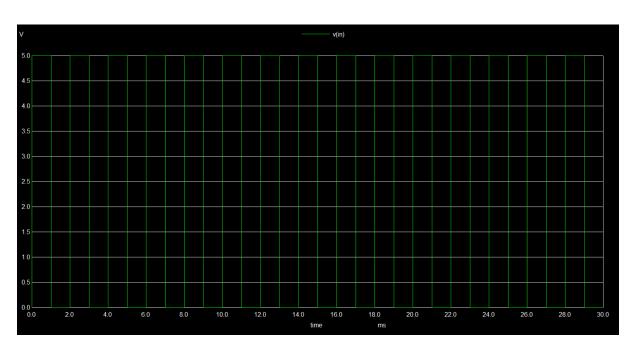

Figure 7.5: Input plot of the L601

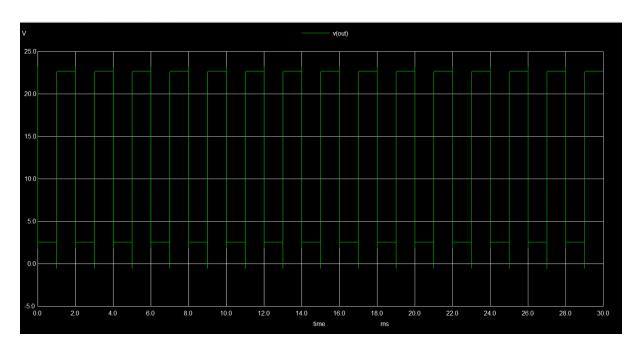

## 7.9 Output Plot

# SN54LS30

#### 8.1 General Description

The SN54LS30 is an 8-input positive NAND gate, meaning it performs the NAND logic function on eight input signals. This IC is part of the Low Power Schottky (LS) TTL logic family, ensuring fast switching speeds with reduced power dissipation. It is widely used in high-reliability applications, particularly in industrial and military environments, due to its extended temperature range.

#### 8.2 Key Features

- Wide Operating Voltage : Standard TTL 5V logic compatibility.

- Extended Temperature Range : -55°C to 125°C

- Low Power Dissipation: Ideal for power-sensitive applications.

#### 8.3 Applications

- Complex Logic Implementations: Reduces the need for multiple smaller NAND gates.

- Address Decoding : Used in memory and peripheral selection circuits.

- Industrial and Military Applications: Reliable operation in harsh environments.

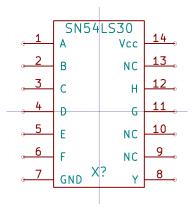

- 8.4 Pin Configuration

Figure 8.1: Pin Configuration of SN54LS30

## 8.5 IC Layout

Figure 8.2: IC Layout of the SN54LS30

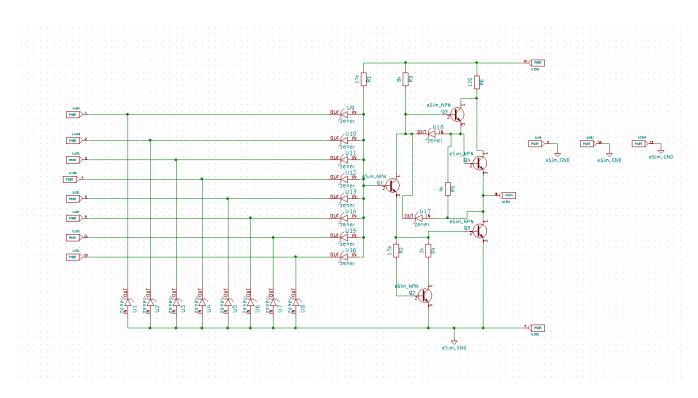

## 8.6 Subcircuit Schematic Diagram

Figure 8.3: Subcircuit Schematic of the SN54LS30

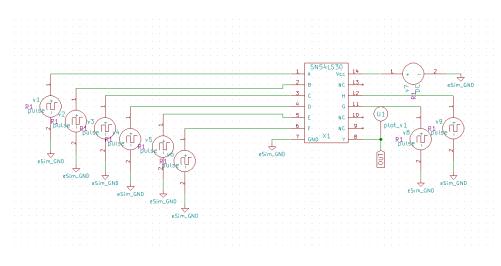

## 8.7 Test Circuit

Figure 8.4: Test Circuit of the SN54LS30

Figure 8.5: HIGH Output of the SN54LS30

## 8.9 Output Plot LOW

Figure 8.6: LOW Output of the SN54LS30

# Failed Circuits

#### 9.1 Overview

In this section, we discuss circuits that did not perform as expected during testing.Understanding the reasons for these failures helps in diagnosing issues and improving circuit design. Each failed circuit is analyzed to identify the potential causes of failure and to suggest corrective measures.

## 9.2 LP2954

## Circuit Diagram

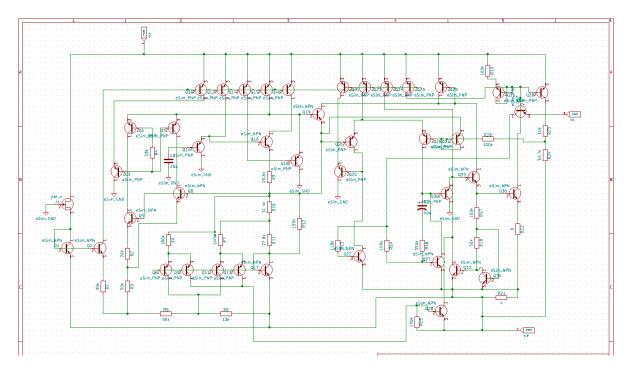

Figure 9.1: Subcircuit Schematic of the LP2954

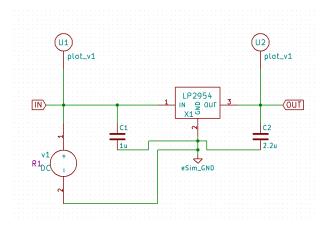

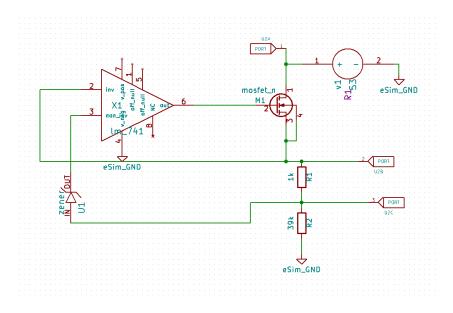

Figure 9.2: Test Circuit of the LP2954

## **Issue Description**

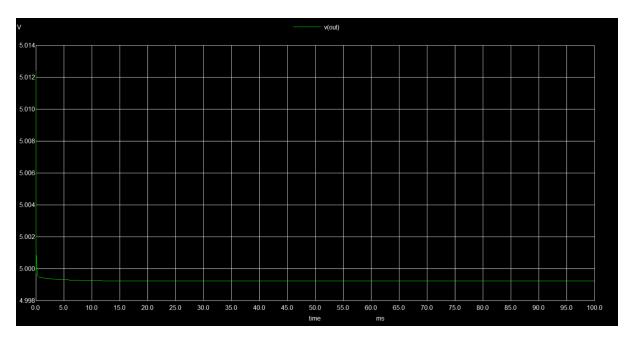

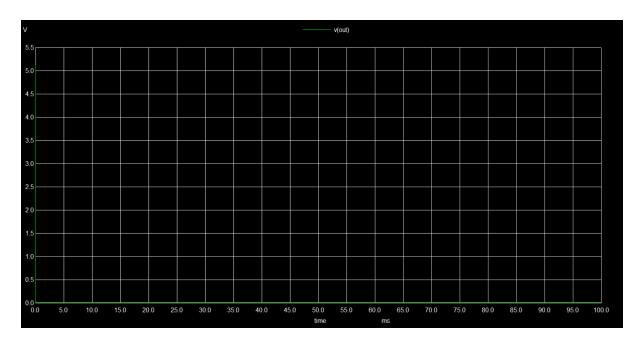

The LP2954 is a low-dropout (LDO) 5V regulator, meaning that with an input of 30V, the output should ideally be regulated at 5V (assuming proper circuit conditions). The LP2954 should regulate to 5V, but it appears to be allowing a much higher output.possible reasons are if the load is too high (low resistance), the regulator might not function properly.

## 9.3 OP470

## Circuit Diagram

Figure 9.3: Subcircuit Schematic of the OP470

Figure 9.4: Test Circuit of the OP470

## **Issue Description**

The formula given is Vout =  $1000 \times \text{Vin}$ . With Vin 1 mV, the expected output voltage should be Vout 1000 mV (or 1V). The output voltage is around -166.83 mV, which is significantly lower than the expected 1V. The OP470 model parameters might be incorrect. The phase inversion suggests an issue with the circuit configuration.

## 9.4 TL783

Circuit Diagram

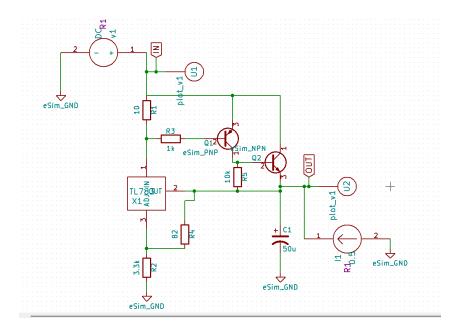

Figure 9.5: Subcircuit Schematic of the TL783

Figure 9.6: Test Circuit of the TL783

## **Issue Description**

The output voltage (Vout) is expected to be 50V, but the simulation shows it fluctuating around 67.53V with noise. Possible causes are Incorrect resistor values in the voltage-setting network, Instability due to improper feedback compensation, Insufficient capacitor filtering, leading to high-frequency noise. Mismatch between TL783 and the transistor gain, causing erratic behavior.

## **Conclusion and Future Scope**

The project achieved its objective of developing a wide range of subcircuits for both Analog and Digital Integrated Circuits, with each IC model meticulously crafted based on the specifications provided in their official datasheets. Through rigorous testing and verification using corresponding test circuits, these IC models were validated for accuracy and functionality. The components developed under this fellowship encompass fundamental circuit elements such as Operational Amplifiers (Op-Amps), Voltage Regulators, Precision Rectifiers, Schmitt Triggers, Differential Amplifiers, Instrumentation Amplifiers, Comparators, Multiplexers, De-Multiplexers, and various Logic Gate ICs. These models are now ready for integration into the eSim subcircuit library, providing a robust resource for developers, students, and researchers. The inclusion of these models in the eSim library will significantly enhance the tool's capabilities, enabling users to easily incorporate these fundamental ICs into their own projects and circuit designs. Looking ahead, this project sets the foundation for the continued expansion of eSim's device model library. We anticipate that more such ready-to-use IC models will be developed, broadening the scope of available components and further empowering the eSim community. This ongoing development will not only aid in academic and research endeavors but also contribute to the growing ecosystem of open-source electronic design automation (EDA) tools.

# **Circuits Contribution**

This chapter lists all the Integrated Circuits (ICs) contributed during the fellowship. Each IC has been carefully modeled and tested, and is now part of the eSim library. The contributions include both analog and digital ICs, covering a wide range of functionalities.

#### 11.1 Sagarikaa R K List of ICs

- 1. SN5410 Triple 3-Input Positive NAND Gates

- 2. LM431 Adjustable Precision Zener Shunt Regulator

- 3. SN7420 Dual 4-Input Positive NAND Gates

- 4. L601 Darlington Arrays

- 5. SN54LS30 8 Input Positive NAND Gates

- 6. LP2954 5V and Adjustable Micropower Low-Dropout Voltage Regulators (Failed IC)

- 7. OP470 Very Low Noice Quad Operational Amplifier (Failed IC)

- 8. TL783 High Voltage Adjustable Regulator (Failed IC)

## Bibliography

- [1] FOSSEE Official Website https://fossee.in

- [2] eSim Official Website https://esim.fossee.in/

- [3] ALL DATASHEET , SN5410 Datasheet https://www.alldatasheet.com/datasheet-pdf/pdf/ 837639/TI1/SN5410.html

- [4] Texas Instruments, LM431 Datasheet https://www.ti.com/lit/ds/symlink/lm431.pdf? ts=1739380616535&ref\_url=https%253A%252F%252Fwww.ti.com%252Fproduct%252FLM431% 253Fqgpn%253Dlm431

- [5] Texas Instruments, SN7420 Datasheet https://www.ti.com/lit/ds/symlink/sn741s20.pdf? ts=1739380803215&ref\_url=https%253A%252F%252Fwww.ti.com%252Fproduct%252FSN74LS20% 253FkeyMatch%253DSN7420%2526tisearch%253Duniversal\_search

- [6] ALL DATASHEET, L601 Datasheet https://www.alldatasheet.com/datasheet-pdf/pdf/22527/ STMICROELECTRONICS/L601.html

- [7] Texas Instruments, SN54LS30 https://www.ti.com/lit/ds/symlink/sn54ls30.pdf?ts= 1739980303861&ref\_url=https%253A%252F%252Fwww.ti.com%252Fproduct%252FSN54LS30

- [8] Texas Instruments, LP2954 Datasheet https://www.ti.com/lit/ds/symlink/lp2954.pdf? ts=1739381017891&ref\_url=https%253A%252F%252Fwww.ti.com%252Fproduct%252FLP2954% 253FkeyMatch%253DLP2954%2526tisearch%253Duniversal\_search

- [9] ALL DATASHEET, OP470 Datasheet https://www.alldatasheet.com/datasheet-pdf/view/ 49057/AD/OP470.html

- [10] Texas Instruments, TL783 Datasheet https://www.ti.com/lit/ds/symlink/tl783.pdf?ts= 1739428934838&ref\_url=https%253A%252F%252Fwww.mouser.in%252F