## Summer Fellowship Report

On

Cloud Based SoC generator using eSim

Submitted by

Mihir Rana, Narra Hemanth and Ayush Kashyap

Under the guidance of

**Prof.Kannan M. Moudgalya** Chemical Engineering Department IIT Bombay

October 22, 2022

## Acknowledgment

It is a pleasure to acknowledge the help and support that has gone in making this successful project. We express sincere gratitude to Kunal Ghosh (VLSI system design) and FOSSEE Team at IIT Bombay for providing me with this opportunity to work on this project and having faith in my abilities. We would also like to thank the eSim team for giving me such a great opportunity of learning and also for enabling me for their help in offering me the resources and guiding me throughout the project. A special thanks to all my mentors, Sumanto Kar, Rahul Paknikar, and Nagesh Karmali for helping me throughout the internship, sharing a lot of valuable and constructive suggestions during the internship. Finally, We wish to thank our parents for consistently encouraging us and keeping us positive at all times.

## Contents

| 1        | Intr           | oduction                                                               | <b>5</b> |

|----------|----------------|------------------------------------------------------------------------|----------|

|          | 1.1            | eSim                                                                   | 5        |

|          | 1.2            | Ngspice                                                                | 5        |

|          | 1.3            | Makerchip                                                              | 5        |

| <b>2</b> | Feat           | cures of eSim                                                          | 6        |

| 3        | Pro            | blem Statement                                                         | 7        |

|          | 3.1            | IP Nomenclature table                                                  | 7        |

| 4        | $\mathbf{IPs}$ | done by Mihir Rana                                                     | 10       |

|          | 4.1            | Folded Cascode Amplifier                                               | 10       |

|          |                | 4.1.1 Circuit details                                                  | 10       |

|          | 4.2            | Low Voltage Low Power Amplifier based on MOSFET Darlington             |          |

|          |                | Configuration                                                          | 12       |

|          |                | 4.2.1 Circuit details                                                  | 12       |

|          | 4.3            | Design of IC 741 tester circuit                                        | 14       |

|          |                | 4.3.1 Circuit details                                                  | 14       |

|          | 4.4            | Design of Half Adder using CMOS technology                             | 16       |

|          |                | 4.4.1 Circuit details                                                  | 16       |

|          | 4.5            | Design of Approximate compressors                                      | 18       |

|          |                | 4.5.1 Circuit details                                                  | 18       |

|          | 4.6            | Design and Analysis of Dickson Charge Pump using CMOS technology       |          |

|          |                | 4.6.1 Circuit details                                                  | 20       |

|          | 4.7            | Low Power CMOS Analog Multiplier using skywater 130nm pdk              | 22       |

|          |                | 4.7.1 Circuit details                                                  | 22       |

|          | 4.8            | Darlington amplifier                                                   | 24       |

|          | 1.0            | 4.8.1 Circuit details                                                  | 24       |

|          | 4.9            | 2:4 Decoder using mixed logic CMOS gates                               | 26       |

|          | 1 10           | 4.9.1 Circuit details                                                  |          |

|          | 4.10           | Implementation of Full Adder using SkyWater 130nm PDK                  |          |

|          | 4 1 1          | 4.10.1 Circuit details                                                 | 28       |

|          | 4.11           | The Two Stage CMOS Operational Amplifier with Frequency Com-           | 20       |

|          |                | pensation                                                              | 30       |

|          | 1 10           |                                                                        | 30<br>20 |

|          | 4.12           | Designing and Plotting the characteristics of a Cascode Current Mirror |          |

|          |                | 4.12.1 Circuit details                                                 | 32       |

|          | 4.13                       | Full wave Bridge rectifier using CMOS                                                                                                                         | 34         |

|----------|----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

|          |                            | 4.13.1 Circuit details                                                                                                                                        |            |

|          | 4.14                       | CMOS Rail-to-Rail Operational Amplifier                                                                                                                       | 36         |

|          |                            | 4.14.1 Circuit details                                                                                                                                        | 36         |

|          | 4.15                       | RC Phase Shift Oscillator using FET                                                                                                                           | 38         |

|          |                            | 4.15.1 Circuit details                                                                                                                                        | 38         |

|          | 4.16                       | Ring Oscillator Using Sky130                                                                                                                                  | 40         |

|          |                            | 4.16.1 Circuit details                                                                                                                                        | 40         |

|          | 4.17                       | Miller compensated two stage operational amplifier                                                                                                            | 42         |

|          |                            | 4.17.1 Circuit details                                                                                                                                        | 42         |

|          | 4.18                       | Current mode logic CML latch                                                                                                                                  | 44         |

|          |                            | 4.18.1 Circuit details                                                                                                                                        | 44         |

|          | 4.19                       | High Efficiency Dc-Dc Buck Boost Converter                                                                                                                    | 46         |

|          |                            | 4.19.1 Circuit details                                                                                                                                        | 46         |

|          | 4.20                       | Gilbert Multiplier Cell                                                                                                                                       | 48         |

|          |                            | 4.20.1 Circuit details                                                                                                                                        | 48         |

|          | 4.21                       | 32-bit ALU                                                                                                                                                    | 50         |

|          |                            | 4.21.1 Circuit details                                                                                                                                        | 50         |

|          | 4.22                       | Full Adder using CMOS                                                                                                                                         | 52         |

|          |                            | $4.22.1 Circuit details \ldots \ldots$ | 52         |

|          | 4.23                       | Full Adder implementation on Dynamic CMOS Logic                                                                                                               | 54         |

|          |                            | 4.23.1 Circuit details                                                                                                                                        | 54         |

|          | 4.24                       | CMOS SCHMITT TRIGGER                                                                                                                                          | 56         |

|          |                            | 4.24.1 Circuit details                                                                                                                                        | 56         |

| <b>5</b> | $\mathbf{TD}_{\mathbf{T}}$ | dono by Ayush Kashyan                                                                                                                                         | 58         |

| 9        | 5.1                        | done by Ayush Kashyap<br>Ideal Circuit:Design of low transconductance OTA                                                                                     | <b>58</b>  |

|          | 0.1                        | 5.1.1 Circuit details                                                                                                                                         | $58 \\ 58$ |

|          | 5.2                        | RING OSCILLATOR                                                                                                                                               | 60         |

|          | 0.2                        | 5.2.1 Circuit details                                                                                                                                         | 60         |

|          | 5.3                        | CMOS Differential cascade voltage switch logic(DCVSL) XOR-XNOR                                                                                                |            |

|          | 0.0                        | 5.3.1 Circuit details                                                                                                                                         | 61         |

|          | 5.4                        | Low Noise Low Power Amplifier for Biomedical Applications                                                                                                     | 63         |

|          | 0.1                        | 5.4.1 Circuit details                                                                                                                                         | 63         |

|          | 5.5                        | ONE BIT MIRROR ADDER                                                                                                                                          | 64         |

|          | 0.0                        | 5.5.1 Circuit details                                                                                                                                         | 64         |

|          | 5.6                        | MIRROR WITH MULTIPLE OUTPUTS                                                                                                                                  | 66         |

|          | 0.0                        | 5.6.1 Circuit details                                                                                                                                         | 66         |

|          |                            |                                                                                                                                                               |            |

| 6        | $\mathbf{IPs}$             | done by Narra Hemanth                                                                                                                                         | <b>68</b>  |

|          | 6.1                        | THREE PHASE INVERTER                                                                                                                                          | 68         |

|          |                            | 6.1.1 Circuit details                                                                                                                                         | 68         |

|          | 6.2                        | Low power and High speed 1 bit full adder circuit                                                                                                             | 70         |

|          |                            | 6.2.1 Circuit details                                                                                                                                         | 70         |

|          | 6.3                        | Sziklai Pair Amplifier                                                                                                                                        | 72         |

|          |                            | 6.3.1 Circuit details                                                                                                                                         | 72         |

|          | 6.4                        | Implementation of a 3-bit CMOS Wallace Tree Multiplier                                                                                                        | 73         |

|      | 6.4.1 Circuit details                                              | 73  |

|------|--------------------------------------------------------------------|-----|

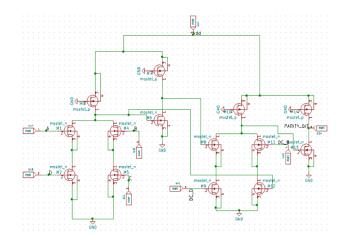

| 6.5  | Low Voltage CMOS Schmitt Trigger                                   | 75  |

|      | 6.5.1 Circuit details                                              | 75  |

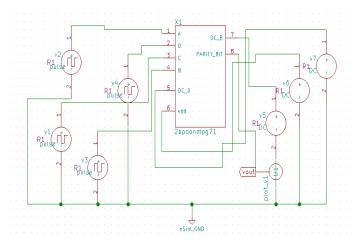

| 6.6  | Design of 8 bit Parity Generator using Pseudo NMOS logic           | 77  |

|      | 6.6.1 Circuit details                                              | 77  |

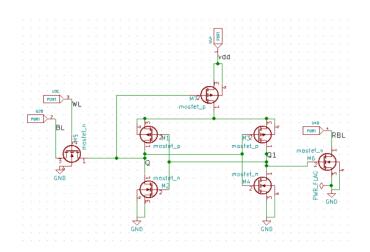

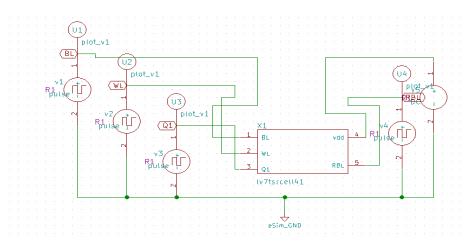

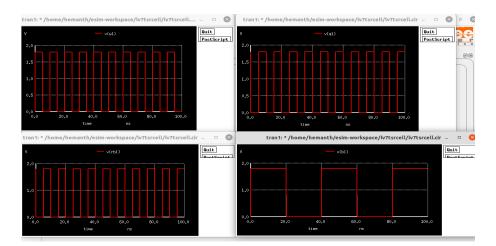

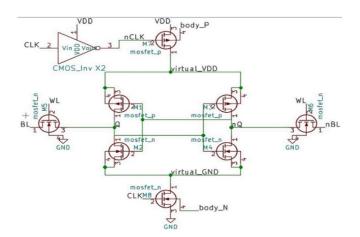

| 6.7  | A Low Power 7T SRAM cell using Supply Feedback Technique CMOS      | 79  |

|      | 6.7.1 Circuit details                                              | 79  |

| 6.8  | Dynamic charge sharing comparator                                  | 81  |

|      | 6.8.1 Circuit details                                              | 81  |

| 6.9  | 1-bit NP-CMOS Dynamic Full Adder                                   | 83  |

|      | 6.9.1 Circuit details                                              | 83  |

| 6.10 | FULL ADDER USING CMOS                                              | 85  |

|      | 6.10.1 Circuit details                                             | 85  |

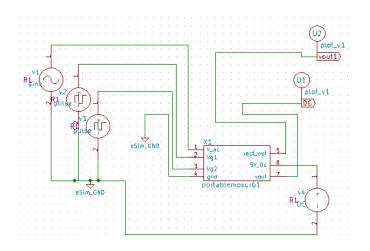

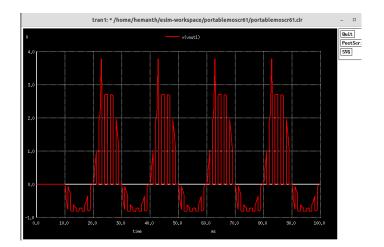

| 6.11 | Portable Mobile Charger for outdoor trips                          | 87  |

|      | 6.11.1 Circuit details                                             | 87  |

| 6.12 | NMOS Schmitt trigger SRAM                                          | 89  |

|      | 6.12.1 Circuit details                                             | 89  |

| 6.13 | 3 Stage CMOS Ring Oscillator                                       | 91  |

|      | 6.13.1 Circuit details                                             | 91  |

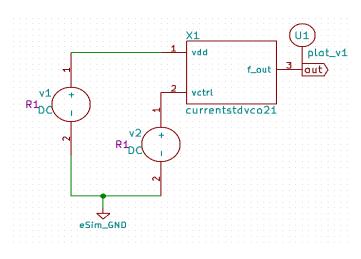

| 6.14 | CURRENT STARVED VCO TARGETING                                      | 93  |

|      | 6.14.1 Circuit details                                             | 93  |

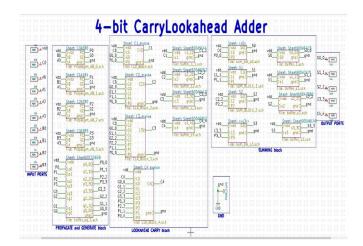

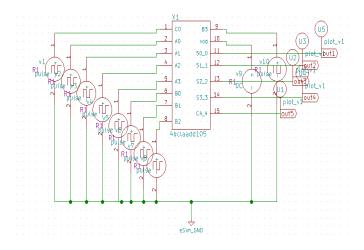

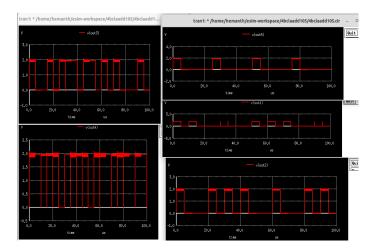

| 6.15 | 4-bit Carry Lookahead Adder                                        | 95  |

|      | 6.15.1 Circuit details                                             | 95  |

| 6.16 | Schmitt Trigger                                                    | 97  |

|      | 6.16.1 Circuit details                                             | 97  |

| 6.17 | 8x4 right Barrel Shifter using NMOS pass transistor logic          | 99  |

|      | 6.17.1 Circuit details                                             | 99  |

| 6.18 | Two Stage CMOS Operational Amplifier                               | 101 |

|      | 6.18.1 Circuit details                                             | 101 |

| 6.19 | Bandgap reference circuit using simple current mirror architecture | 103 |

|      | 6.19.1 Circuit details                                             | 103 |

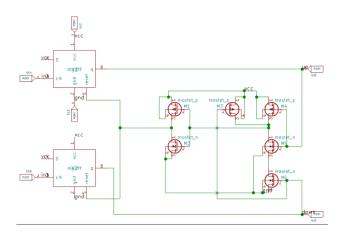

| 6.20 | Design and Analysis of DIBO Differential Amplifier                 | 105 |

|      | 6.20.1 Circuit details                                             | 105 |

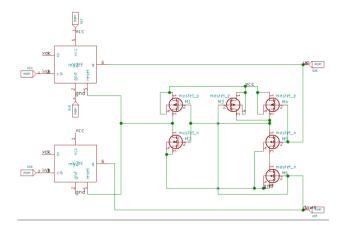

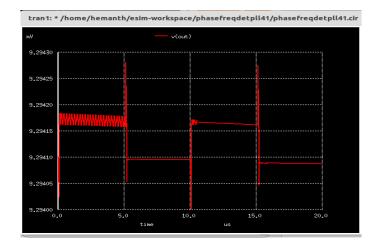

| 6.21 | Phase Frequency Detector for Phase locked loops                    | 107 |

|      | 6.21.1 Circuit details                                             | 107 |

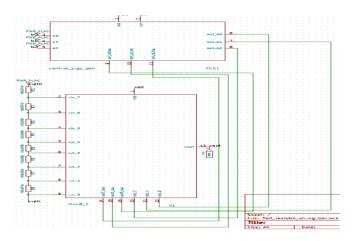

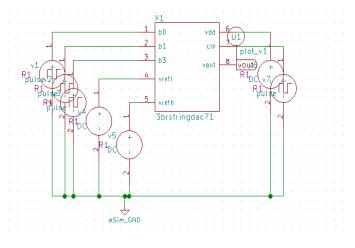

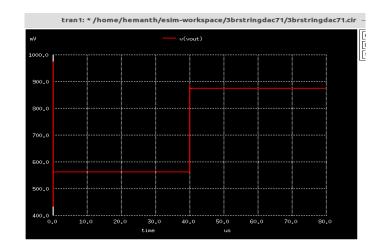

| 6.22 | 3-bit resistor string DAC                                          | 109 |

|      | 6.22.1 Circuit details                                             | 109 |

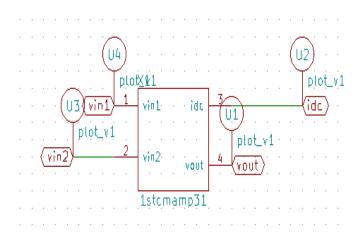

| 6.23 | Single Stage Operational Amplifier Using CMOS                      |     |

|      | 6.23.1 Circuit details                                             |     |

| 6.24 | Low Power SRAM Cell                                                | 113 |

|      | 6.24.1 Circuit details                                             | 113 |

# Chapter 1 Introduction

### 1.1 eSim

eSim is a free/libre and open source EDA tool for circuit design, simulation, analysis and PCB design developed by FOSSEE, IIT Bombay. It is an integrated tool built using free/libre and open source software such as KiCad, Ngspice, NGHDL and GHDL.

## 1.2 Ngspice

ngspice is the open source spice simulator for electric and electronic circuits. Such a circuit may comprise JFETs, bipolar and MOS transistors, passive elements like R, L, or C, diodes, transmission lines and other devices, all interconnected in a netlist. Digital circuits are simulated as well, event driven and fast, from single gates to complex circuits. And you may enter the combination of both analog and digital as a mixed-signal circuit. ngspice offers a wealth of device models for active, passive, analog, and digital elements. Model parameters are provided by our collections, by the semiconductor device manufacturers, or from semiconductor foundries. The user adds her circuits as a netlist, and the output is one or more graphs of currents, voltages and other electrical quantities or is saved in a data file.

## 1.3 Makerchip

Makerchip provides free and instant access to the latest tools directly from your browser and from your desktop. This includes open-source tools and proprietary ones. You can code, compile, simulate, and debug Verilog designs, all from your browser. Your code, block diagrams, waveforms, and novel visualization capabilities are tightly integrated for a seamless design experience. While Makerchip introduces ground-breaking capabilities for advanced Verilog design, it also makes circuit design easy and fun!

## Chapter 2

## Features of eSim

- Draw circuits using KiCad, create a netlist and simulate using Ngspice.

- Design PCB layouts and generate Gerber files using KiCad.

- Add/Edit device models(Spice Models) and subcircuits using the Model Builder and Subcircuit Builder tools.

- Perform Mixed-Signal Simulation.

- Support for Ubuntu and Windows OS.

- Interface with OpenModelica modelling software.

## Chapter 3

## **Problem Statement**

The task was to Verify the Analog IP's and check the functionality of the circuit, study about the circuit. After verifying the functionality we have to convert IP into a sub-circuit which is later ported into esim and can be used as an esim component. To solve the confusion in the IP nomenclature, we have created a standard nomenclature for shortened names.

### 3.1 IP Nomenclature table

| Original name    | Shortened name |

|------------------|----------------|

| cmos             | cm             |

| full             | f              |

| adder            | add            |

| nmos             | nm             |

| pmos             | pm             |

| amplifier        | amp            |

| bit              | b              |

| schmitt          | smt            |

| low              | 1              |

| high             | h              |

| speed            | spd            |

| power            | р              |

| tester           | tstr           |

| oscillator       | osci           |

| buck boost       | bb             |

| converter        | convtr         |

| full wave        | fw             |

| bridge           | bg             |

| low voltage      | low power      |

| rail to rail     | rr             |

| pseudo           | pdo            |

| parity generator | pg             |

| trigger          | trigger        |

| Table $3.1$ : | <b>IP</b> Nomenclature | table |

|---------------|------------------------|-------|

|---------------|------------------------|-------|

| Original name             | Shortened name       |

|---------------------------|----------------------|

| stage                     | st                   |

| carry look ahead          | cla                  |

| dynamic                   | dym                  |

| charge sharing            | CS                   |

| comparator                | comp                 |

| sramcell                  | srcell               |

| barrel shifter            | barsft               |

| stage                     | stg or st            |

| cross                     | x                    |

| decoder                   | dec                  |

| Approximate               | aprx                 |

| Compressor                | cmprsr               |

| Sziklai Pair              | sp                   |

| Analog                    | a                    |

| Digital                   | d                    |

| Multiplier                | mult                 |

| resistor                  | r                    |

| phase locked loop         | pll                  |

| detector                  | det                  |

| frequency                 | freq                 |

| gilbert                   | gbrt                 |

| Current mode logic        | cml                  |

| latch                     | latch                |

| dickson                   | dickson              |

| pump                      | pmp                  |

| charge                    | с                    |

| inverter                  | inv                  |

| wallace tree              | wall tree            |

| portable                  | portable             |

| charger                   | cr                   |

| Bandgap voltage reference | bgvr                 |

| Frequency compensated     | fc                   |

| starved                   | $\operatorname{std}$ |

| cascode                   | csde                 |

| Mirror                    | mirror               |

| Folded Cascode            | fcsde                |

| Miller Compensated        | mc                   |

Table 3.2: IP Nomenclature table

## Chapter 4

## IPs done by Mihir Rana

### 4.1 Folded Cascode Amplifier

#### 4.1.1 Circuit details

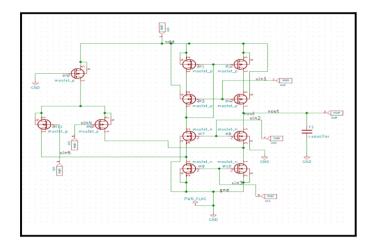

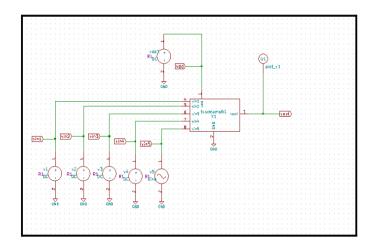

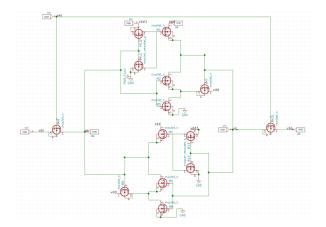

It is well known that the active cascade gain boosting technique can be used to increase the DC gain of an Op Amp without degrading its high frequency performance. Unfortunately the existence of pole zero doublet will unfavorably affect the settling performance of the gain boosted Op Amp and the effort of pushing up the doublet can raise stability problem. Also in correlated double sampling(CDS) and correlated level shifting (CLS) methods two clock cycles are needed to amplify so the speed may be reduced. The new structure proposed in this paper is based on the conventional folded cascade amplifier. Folded cascode amplifier is a single-pole operational amplifier with a large output swing and has a higher gain compared to the ordinary op amp. It is very suitable for deep negative feedback because of its small signal gain that can be very large. Comparing to the ordinary telescopic amplifiers, folded cascode operational amplifiers have a larger output swing. To increase the DC gain of the Op Amp a new method is presented that uses positive feedback concept. Opposite to conventional techniques this technique does not add extra nodes to the structure of the Op Amp or pole zero doublet to the transfer function of the Op Amp. The folded cascade configuration achieves output impedance comparable to that of a normal telescopic amplifier with lesser number of devices stacked between supplies and ground in the output stage.

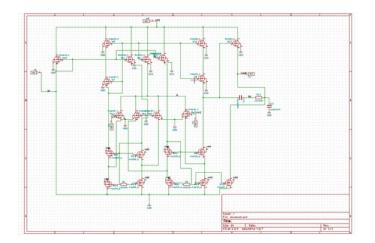

Figure 4.1: Circuit diagram

Figure 4.2: Sub-circuit

Figure 4.3: Output waveforms

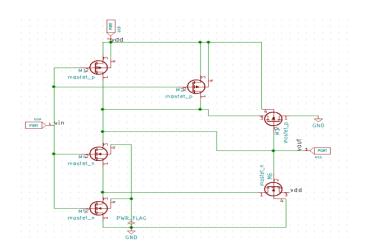

## 4.2 Low Voltage Low Power Amplifier based on MOSFET Darlington Configuration

#### 4.2.1 Circuit details

The Amplifier which we proposed to be taken is based on MOSFET Darlington pair configuration can be done by using both NMOS transistors or PMOS transistors. The Circuit is designed by using two NMOS or PMOS transistors, DC biasing voltage, Resistors, Capacitors, Input AC voltage source. Here, MOS transistors Q1, Q2 can be used as per requirement. And by considering the value of low dc voltage applied consumption of power is very important to be low while the output power is also low. By giving AC source voltage as Vin. The source voltage will have a phase value, we should give the input frequency and the Amplitude value of voltage taken. Resistors used are Input Resistor (R1), Source Resistor 1 (RS1), Source Resistor 2 (RS2), Drain Resistor (RD), LOAD Resistor (RL). Capacitors used are Input Capacitor CC1, Output Capacitor CC2, Source Capacitor CS. DC biasing voltage (VDD) is the supply dc voltage to the circuit. And the value of dc voltage is low so the output power will be low so by reducing the power consumption (PC) we can get the maximum output power. Now the two MOS transistors are connected through the wire with some resistors and capacitors are connected. And, the DC biasing voltage can be connected to the drain resistor and Q1 transistor through the wire. And then the dc analysis of the circuit can be done (applying dc voltage or current). By performing dc analysis, we come to know that what is the behavior of the circuit which we are taken. Here, in this circuit output is taken across the LOAD resistor (RL).

Figure 4.4: Circuit diagram

Figure 4.5: Sub-circuit

Figure 4.6: Output waveforms

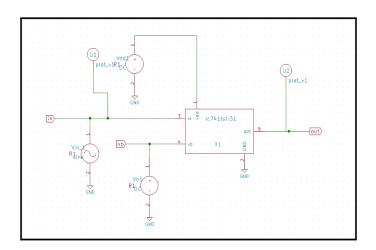

### 4.3 Design of IC 741 tester circuit

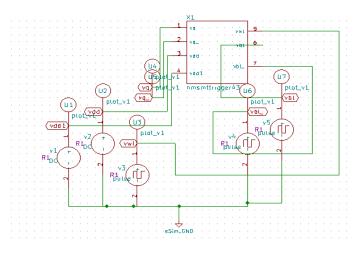

#### 4.3.1 Circuit details

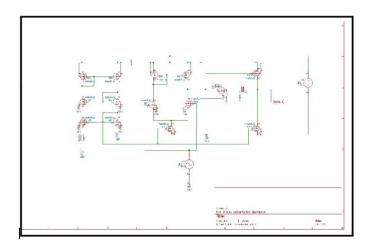

1) Differential input stage: The importance of differential amplifier is to amplify the difference between two input signals. A slight difference in input signals leads to high gain at output. 2) Gain stage: Darlington transistor pair used to provide required gain 3) Output stage: Class AB complementary push-pull We can replace those two diodes with a transistor In this circuit Pin 3 (non-inverting) is kept constant and Pin 2(inverting) is getting changed due to the capacitor (C1). When the capacitor C1 starts charging Voltage at pin 3 is more than pin 2, so led starts blinking. Capacitor C1 is getting charged through R4 resistor. When the Capacitor gets full charged led becomes low. Again when Capacitor is getting charged and voltage at pin 2 is less than that the led starts blinking again. This on off will generates the square waveform at the output side. If Led doesn't blink at fixed intervals then we can't get the square waveform so that the IC which we are testing is decided as faulty. 1) Connect voltage supply of 9V to pin 7 and 0V to pin 4 2) Take Vcc=9 (volts) and Vee=0V 3) Connect both the pin4 and pin 7 to ground. Now the output voltage should be 0V 3) Now, connect the pin7 alone to Vcc(9V). The output should now be 9V 4) Now repeat the same with pin4 the output should be 9V.

Figure 4.7: Circuit diagram

Figure 4.8: Sub-circuit

Figure 4.9: Output waveforms

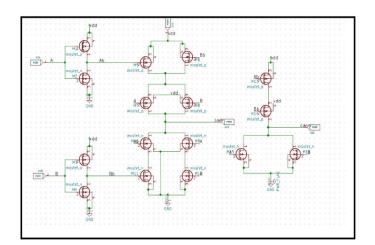

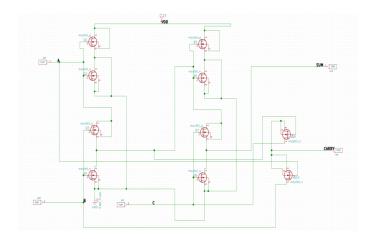

### 4.4 Design of Half Adder using CMOS technology

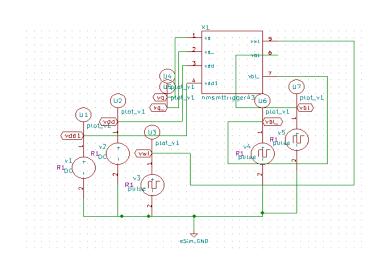

#### 4.4.1 Circuit details

Half adder is a combinational circuit that performs simple addition of two single bit binary numbers and produces a 2-bit number. The LSB of the result is the sum and the MSB is the Carry. In the basic approach the half adder is implemented using the primitive logic gates i.e., XOR and AND for sum and carry respectively. Here in the project Half adder is implemented using the principle of the static (CMOS) technology. This helps us in making the size of fabrication more small in terms of nanometre and hence making it compact yet efficient. The (CMOS) comprises of (NMOS) and (PMOS). There are two inputs and two outputs in a Half Adder. Inputs are named as A and B, and the outputs are named as Sum (S) and Carry (C). The appropriate sum and carry logic is realised and the circuit is represented using pull up and pull down transistors i.e. pmos and nmos transistors for the logic. The circuit for sum and carry are separately implemented in the same schematic. Required Inputs are inverted using pmos and nmos inverter design .Here in the circuit the inputs A and B are inverted using the inverter circuit, Ab and Bb are the other two inputs obtained using these respective logic are generated for sum and carry. Required ground and power supply is provided in the circuit. The circuit is annotated and the Netlist is generated using eSim. The python plot for sum and carry are obtained along with ngspice inputs A, B.

Figure 4.10: Circuit diagram

Figure 4.11: Sub-circuit

Figure 4.12: Output waveforms

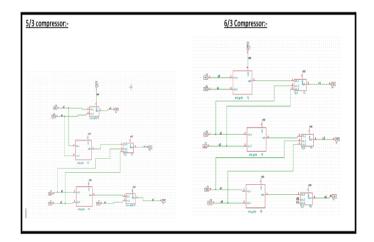

### 4.5 Design of Approximate compressors

#### 4.5.1 Circuit details

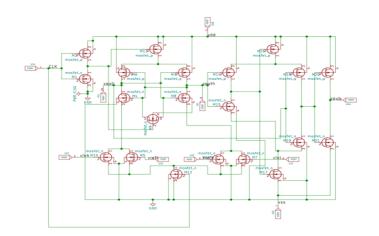

A compressor is a logic circuit that counts the number of ones in the input. Approximate compressor have j inputs and compute j/2 outputs by using novel approach aimed to minimize the error probability and the average error. The outputs of proposed approximate compressors do not have carry outputs this is different from standard compressors which consists of carry. In this design we implementing 5/3compressor i.e 5 inputs and 3 outputs 6/3 compressor i.e 6 inputs and 3 outputs These approximate compressors implemented using AND and OR gates For AND. gate, whenever both inputs are high then output will be high otherwise output will be low and For OR gate, whenever both inputs are low then output will be low otherwise output will be high. We can also use higher order compressors i.e 7/4 8/4 9/510/5 11/6 12/6 13/7 14/7 15/8 16/8 17/9 18/9 19/10 20/10 etc. These higher order compressors are implemented using  $2/1 \ 3/2 \ 4/2 \ 5/3 \ 6/3$ . The output of the multiplier are divided into two parts MSB and LSB. The LSB bits are given to the approximate compressors and MSB bits are given to exact compressors. The output from both compressors are given to the adder circuit for multiplier output includes sum and carry outputs. Approximate compressors are used in the least-significant bits of the multiplier outputs. The approximate multiplier produces output which is approximately equal to the exact multiplier output.

Figure 4.13: Circuit diagram

Figure 4.14: Sub-circuit

Figure 4.15: Output waveforms

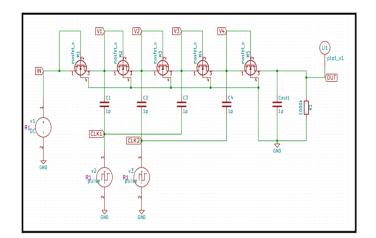

## 4.6 Design and Analysis of Dickson Charge Pump using CMOS technology

#### 4.6.1 Circuit details

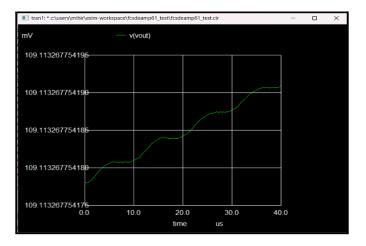

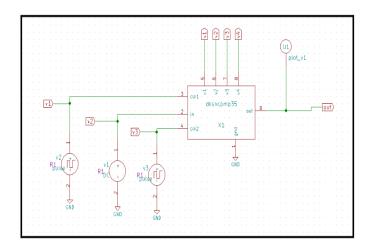

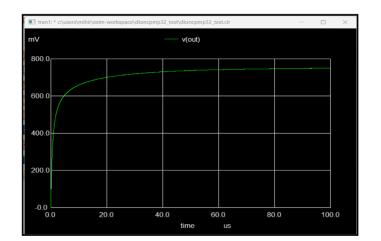

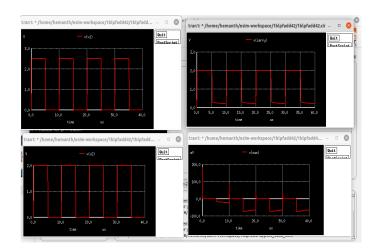

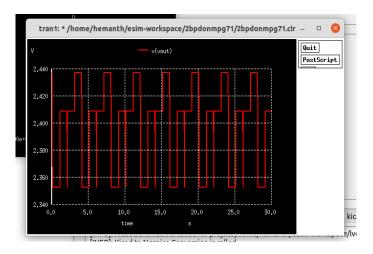

The Dickson Charge Pump consists of the pumping capacitors which are arranged in a parallel fashion, which reduces the output impedance and increases the voltage gain as the number of stages increases. A diode-connected NMOS transistor is used for the construction of this CP. Here Vdd is the power supply voltage, NMOS transistor acts as switches, and V1 is the node voltage at the upper plate of the capacitor. Two clock sources Clk1 and Clk2 which have the same peak voltage, complementary phase, and are non-overlapping are applied to each stage in an alternative manner. When Clk1 is low, Clk2 will be high due to the complementary phase and subsequently, the switch MD1 is turned ON and the first capacitor is charged by the voltage source Vdd to the maximum voltage of Vdd - Vt at node V1. In the next half clock, MD1 turns OFF, and the voltage Vdd provided by the Clk1, gets added to the voltage Vdd - Vt which is already present, and as a result, the voltage at node V2 becomes 2Vdd - Vt. At the same period, the switch MD2 becomes ON and the next capacitor is charged through MD2 by the voltage 2Vdd-Vt, to a maximum voltage of 2Vdd - 2Vt. In this way, the charge gets pumped from one stage to another and the node voltages at pumping capacitors of higher stages increase continuously. The final capacitor doesn't add any voltage as it is grounded and it smoothens the output. The transient analysis performed to the circuit for a Vdd of 1.8V gave an output between 4.1-4.2V for 7.5us and saturated at 4.8V for a 130nm CMOS process, and the simulation was done using eSim and SKY130 PDK.

Figure 4.16: Circuit diagram

Figure 4.17: Sub-circuit

Figure 4.18: Output waveforms

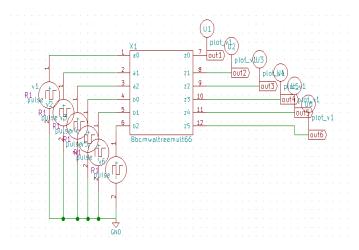

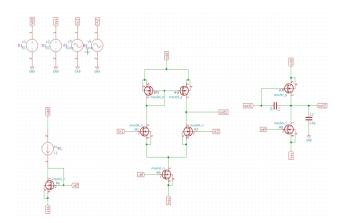

## 4.7 Low Power CMOS Analog Multiplier using skywater 130nm pdk

#### 4.7.1 Circuit details

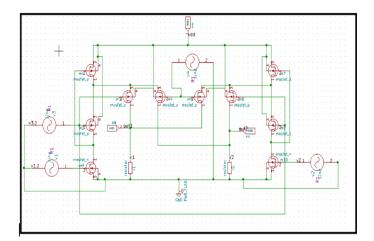

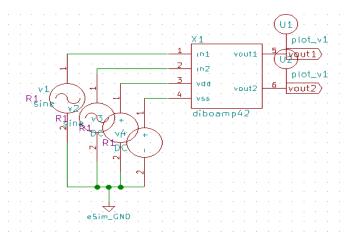

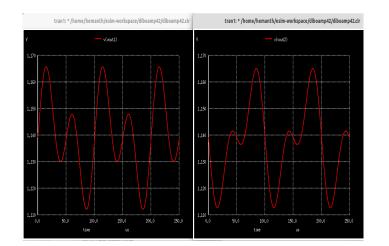

The analog multiplier is used to multiply two continuous input signals, say v1 and v2 and produces output as v which is the linear product of two inputs. The output can be expressed as v=k v1 v2, where k is the gain. The circuit design proposed in this paper is used to eliminate extra voltage reference to provide a compact circuit design. By using CMOS technology with 130nm, the device density and performance can be improved. Low power consumption can be also achieved using the same technology. The circuit consists of a pair of common source amplifier with input transistors m9 and m10. The output is the squared function of input voltages v1 and v2. The circuit is built using 8 PMOSs and 2 NMOSs with two resistors. Transistors of m1 to m8 are of the type PMOS and transistors of m9 and m10 are of the type NMOS. The resistor value is taken as 2.5kOhm to make all the transistors present in the circuit to work in proper region. Transistors m1 to m8 acts as square root circuit in non-linear cancellation path. The output current from the input transistors m9 and m10 are directed into the square root circuit block which results in producing differential output voltage or current which is the multiplication of the input signals v12 and v34. v12 signal is the difference between v1 and v2 input signal, whereas v34 signal is the difference between v3 and v4 input signal. The resulting output signal v is the differential output of vout1 and vout2. The circuit can be able to operate with an input voltage of 1 to 1.2v and the measured power consumption is between 35uW to 98uW.

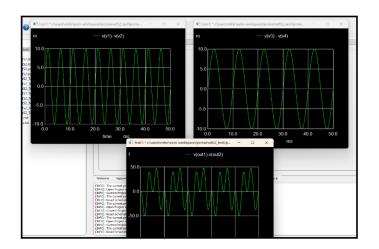

Figure 4.19: Circuit diagram

Figure 4.20: Sub-circuit

Figure 4.21: Output waveforms

### 4.8 Darlington amplifier

#### 4.8.1 Circuit details

we proposed various modifications in small signal pair amplifier circuit and calculated some different results that may be useful for various applications. In comparison to bipolar conventional pair, we can also design a MOSFET configuration to reduce supply voltage (VDD) and dc consumption power. If we increase the collector current in pair amplifier, DC consumption power also increases and noise also increases, we can remove this disadvantage by designing a single input single output (SISO) amplifier based on MOSFET pair configuration. In this design NMOS and PMOS is used wherein here the the output of NMOS is given as the input for PMOS that is CMOS. Some resistances and capacitors are used with different values. One capacitor is used as load capacitor and another one input capacitor is also on this circuit. In electronics, amplifying signal by using pair is very important. The value of resistances used are 22kohm, 5kohm, two 100ohm, two 1kohm. Two capacitors are used in the proposed circuit one at the input terminal and one at the output terminal as a load. and the value of capacitors used are 22u and 1u. Recently Darlington cell and Darlington topology have been reported high gain and good bandwidth for modern application. In transient response time is varying with voltage and current. Other parameters and DC biasing supply that are used to design respective circuits. The performance of pair amplifier is very poor at high frequency and then the output will be verified.

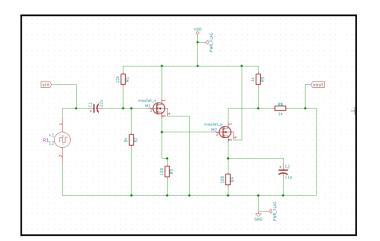

Figure 4.22: Circuit diagram

Figure 4.23: Sub-circuit

Figure 4.24: Output waveforms

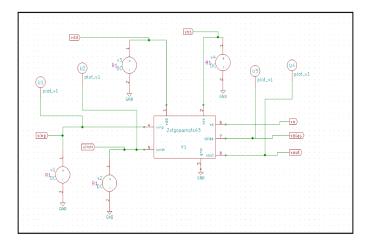

### 4.9 2:4 Decoder using mixed logic CMOS gates

#### 4.9.1 Circuit details

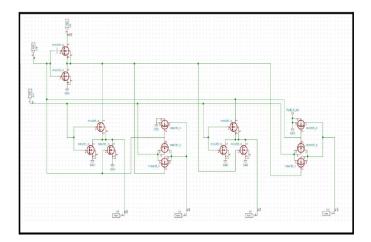

A 2:4 line decoder has two inputs, A and B where A is the MS bit and B is the LS bit. It has four minterm outputs, D0 = A'B', D1 = A'B, D2 = AB' and D3 = AB. It can be designed by using TGL or DVL gates as it takes 16 transistors which includes 12 AND/OR gates and 2 inverters. By using some proper signal arrangement, we can eliminate one of the two inverters A or B; Here D0 and D2 is implemented by using DVL logic, while D1 and D3 is be implemented by using TGL logic. For D0 and D2, A is the propagate signal, and for D1 and D3, B is the propagate signal; this eliminates the inverter B. Hence, the 14-transistor decoder consists of 9 NMOS and 5 PMOS for the low power decoder. The same low power 2:4 decoder can also be realised if we interchange the position of the TGL and DVL of the minterms in the above configuration. This is called inverting topology. Here also the elimination of inverter B is done. Thus, there is overall reduction of two transistors, logical effort, switching activity and also power dissipation in both the topologies. The topologies can be termed as 2:4 LP and 2:4 LPI, I for invert. In our circuit, the 2:4 LP decoder will be implemented and simulated. The necessary circuit diagrams are attached.

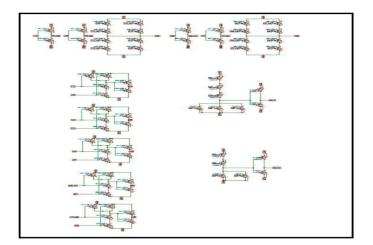

Figure 4.25: Circuit diagram

Figure 4.26: Sub-circuit

Figure 4.27: Output waveforms

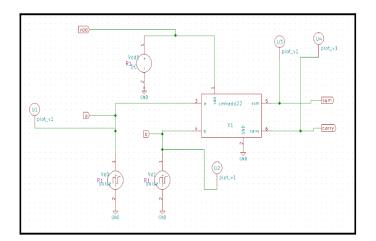

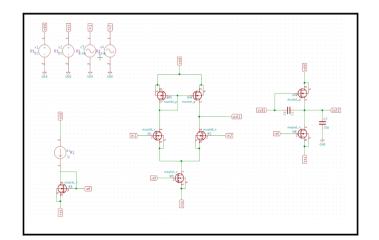

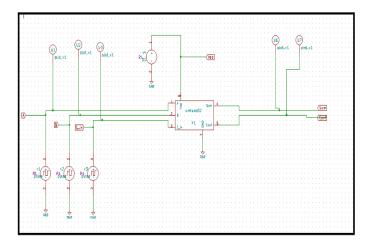

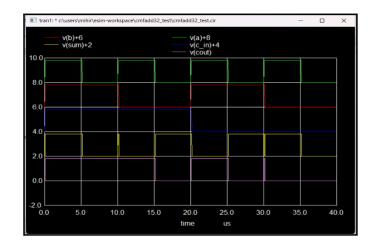

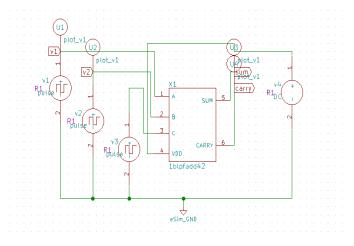

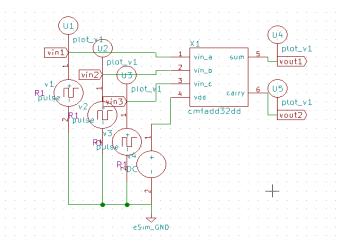

## 4.10 Implementation of Full Adder using SkyWater 130nm PDK

#### 4.10.1 Circuit details

Till today, different types of full adder cell are made and designed with different logic styles in digital world. In that some of them are good low power consumption, some of them for high speed and few for minimum area requirement but all these circuits have its own merits and demerits. According to the required application these full adders are used. Few of the full adder cells which are already implemented are convectional full adder, Static Energy Recovery Full Adder cell, Gate Diffusion Input full adder cell, etc. For most of the complex computational circuit requires full adder are used. Due to this, the whole power consumption and speed of computational circuit can be managed by the implementing the low power and high speed adder cell. So performance is totally depends on full adder. A full adder cell consists of three inputs and two outputs. Some of them are Expression for sum and carry out Sum = A'.b'.Cin + A'.B.Cin' + A.B'.Cin' + A.B.Cin = (A xor B) xor Cin Carry out(Cout) = A'.b.Cin + A.B'.Cin + A.B.Cin' + A.B.Cin = A.B + B.Cin + Cin.A = (A)xor B)  $\operatorname{Cin} + (\operatorname{A} \operatorname{xor} B)$ ' B This circuit is implemented with help of ten transistors. This circuit was implemented by using XOR gate. It uses two XOR module section and one inverter section. Each XOR module section is made by using 2 PMOS and 2 NMOS transistors. This is done which gives a better power and delay when compared to other circuits of full adder.

Figure 4.28: Circuit diagram

Figure 4.29: Sub-circuit

Figure 4.30: Output waveforms

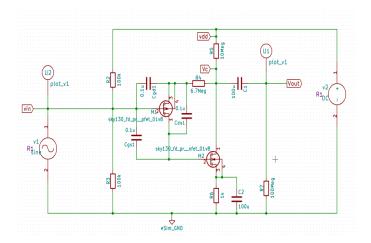

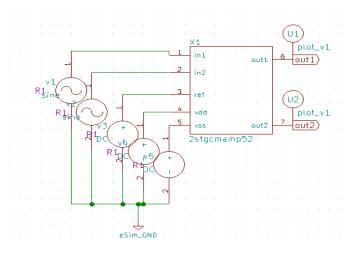

## 4.11 The Two Stage CMOS Operational Amplifier with Frequency Compensation

#### 4.11.1 Circuit details

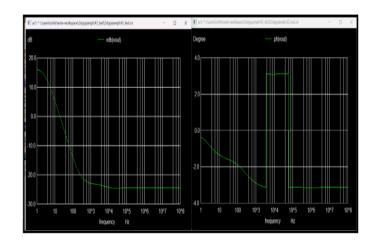

Operational Amplifiers, Op Amps for short are play a very crucial role in the Linear Integrated Circuit Design. It can perform mathematical operations which make it "operational" amplifier, amplifier, comparators, PLLs, Integrators, Filters are few notable circuits that use Op Amp. They play a vital role in biomedical field for amplifying weak biomedical signals, which is important for gaining insights into the signal. The Operational Amplifier design is achieved through skywater 130nm technology. This circuit employs a NMOS differential amplifier M1 and M2 with two input terminals, with a PMOS load M3 and M4. This circuit is provided bias with the help of a current mirror circuit M5 and M6 provided with a constant current source. The output is taken as a single ended output and the gain of the differential amplifier thus obtained is further increased with the help of a Common Source Amplifier M7 which is also biased with the current mirror circuit of M5 and M8. The capacitors provide a stability against the poor phase margin of the circuit by trading off the fast response of the amplifier. Hence for better phase margin an external compensation is a must. The circuit employs different aspect ratio for different MOSFETs for the correct bias and operation of the circuit. The circuit provides a gain of nearly 40dB with a gain bandwidth product of 4.7MHz and about 3KHz 3dB cut off, which makes the operational amplifier circuit to amplifier a 1mV peak to peak to about 2V peak to peak thus weak signals can easily be amplified.

Figure 4.31: Circuit diagram

Figure 4.32: Sub-circuit

Figure 4.33: Output waveforms

## 4.12 Designing and Plotting the characteristics of a Cascode Current Mirror

#### 4.12.1 Circuit details

The intent here is to design the cascode current mirror and study its various characteristics. Herein, this design uses the "cascoding" topology of the transistors. Cascoding can be simply defined as subsequent cascading of two stages, i.e., common source stage and common gate stage. Due to this cascode connection, the overall output impedance of the circuit increases which is also necessary to keep the output current constant. In the process of designing a simple current mirror, we generally ignore the "channel length modulation" effect, and this makes the circuit less accurate. In case of cascode current mirror, along with the simple current mirror circuit, two more MOSFETs are used to ensure the proper matching of the transistors, that means, equal drain-source voltage of the transistors. So, here, in this circuit a Cascode current mirror is implemented using four MOSFETs and its transfer characteristics, i.e., between output current and input current, and the output characteristics, i.e. between output current and supply voltage is plotted and studied. The sizing of the transistor can be done to achieve the desired and accurate results. Also, the region of operation of all the MOSFETs should be "Saturation" and in the results, it is expected that the cascode current mirror should be much more accurate than simple current mirror.

Figure 4.34: Circuit diagram

Figure 4.35: Sub-circuit

Figure 4.36: Output waveforms

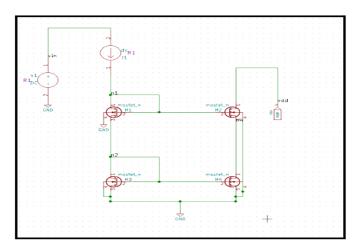

### 4.13 Full wave Bridge rectifier using CMOS

#### 4.13.1 Circuit details

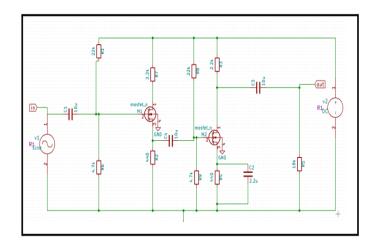

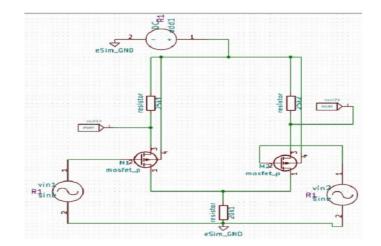

The full wave rectifier circuit used with the combination of full wave rectifier to form a bridge is known as bridge is known a bridge rectifier. A CMOS based rectifier is designed using the MOS transistors which consist of filer and load. For the proper pulsating DC power output supply waveform. A MOS is introduced in the full wave bridge rectifier which act as diodes in the process of rectification. Four MOS are used PM1, PM2, NM1, and NM2 which regulated the power supply current to generate the required output DC supply wave form. When one of the terminal becomes negative, then the other becomes more positive than the other. This means the NM1 assuming the upper part, is turn OFF and PM1 is ON then current is flowing through the PM1 to NM2 to Load and getting pulsating DC output convert sustained output. Similar happens vice versa. Since CMOS has low static power consumption, high noise immunity and very low static power consumption is becomes much more efficient than their counterpart pn junctions diode. For each case the direction of the current is the same, so we have unidirectional current flow, which is DC voltage. The output of this circuit is the rectified signal and a full wave signal. The proposed rectifier circuit has been compared with its conventional rectifier circuit. It explains the efficiency of the proposed circuit which is much improved and increased than its conventional circuit.

Figure 4.37: Circuit diagram

Figure 4.38: Sub-circuit

Figure 4.39: Output waveforms

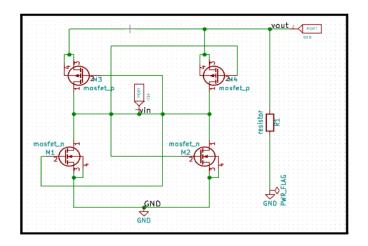

## 4.14 CMOS Rail-to-Rail Operational Amplifier

### 4.14.1 Circuit details

Rail-to-rail op-amps allow signals to swing from negative supply rail to the positive supply rail. Nowadays, rail-torail operational applifiers play a significant role in various biomedical applications. Earlier rail-to-rail op-amps were designed using BJTs, now CMOS technology is utilized. CMOS transistors have an edge over BJT in terms of very high input impedance, high speed, and low leakage current. The topology of the input stage is based on the folded cascade op-amp with a PMOS differential pair and NMOS cascode load. Due to the usage of PMOS transistors at the input terminals, the input voltage can come close to the negative rail. NMOS differential input pairs, unlike PMOS differential input pairs, operate near the positive supply rail. By combining the combination of both configurations, a parallel-connected PMOS and NMOS differential stage reaches operational mode at both rails. The rail-torail output stage reduces voltage drops at the output branch so that the output can reach the rails. The output stage is configured with a common-source NMOS and PMOS connected at the drain. The operating point is one of the most important factors to consider when designing the push-pull inverter output stage. The voltage input of this stage is the output voltage from the preceding stage. Two transistors in the push-pull inverter output stage are in the saturation region at this voltage. The current is largely dependent on the size of the transistors because there is no current bias network.

Figure 4.40: Circuit diagram

Figure 4.41: Sub-circuit

Figure 4.42: Output waveforms

### 4.15 RC Phase Shift Oscillator using FET

### 4.15.1 Circuit details

To create oscillation and sine wave output we need an active component, either Transistor or Op-amp in inverting configuration, and we need to feed back the output of those components to the input through the three pole RC network. It will produce a 360-degree phase shift at the output and produce a sine wave. To build the circuit we need the following things 1. Breadboard 2. 3 pcs of .1uF ceramic capacitors 3. 3 pcs of 680R resistor 4. 2.2k resistor 1 pc 5. 10k resistor 1 pc 6. 100R resistor 1 pc 7. 68k resistor 1 pc 8. 100uF capacitor 1 pc 9. BC549 Transistor 10. 9V power supply The output is provided as the input of the RC-networks which is again provided across the base of the transistor. If By cascading there RC network, we will get 180-degree phase shift. The RC networks are providing the necessary phase shift in the feedback path which is again altered by the transistor. The Phase shift oscillator can be made as variable phase shift oscillator which can produce a wide range of frequencies depending on the pre-set value determined. This can be done easily by changing only the fixed capacitors C1, C2, and C3 with a triple gang variable capacitor. Resistor value should be fixed and same in such cases. The initial starting point of the sinusoidal wave is 0 degree in phase and if we identify each positive and negative peak and 0 points, we will get 90, 180, 270, 360 degree phase. So, when a sinusoidal signal starts it's journey other than the 0-degree reference, we call it phase shifted differentiating from 0-degree reference.

Figure 4.43: Circuit diagram

Figure 4.44: Sub-circuit

Figure 4.45: Output waveforms

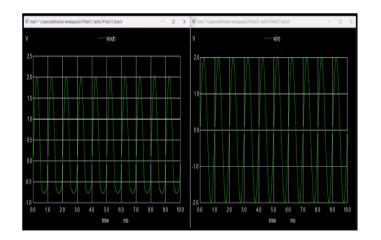

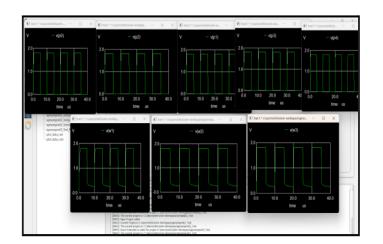

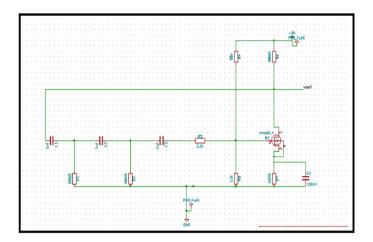

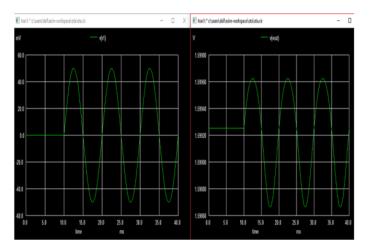

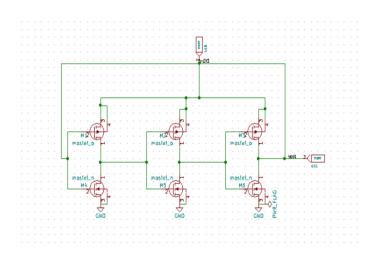

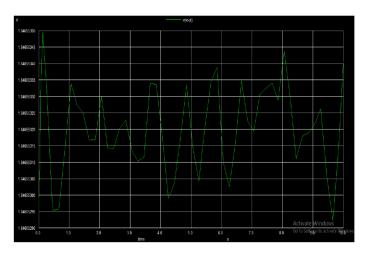

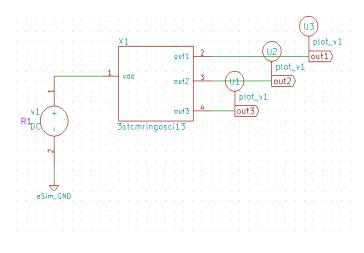

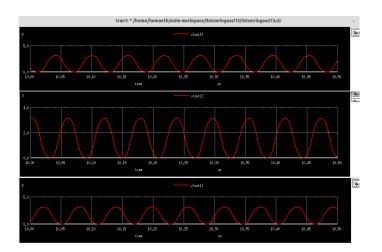

## 4.16 Ring Oscillator Using Sky130

### 4.16.1 Circuit details

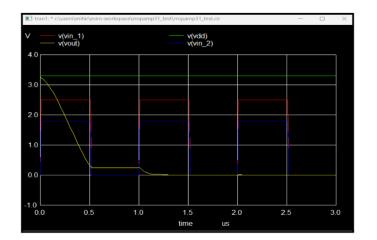

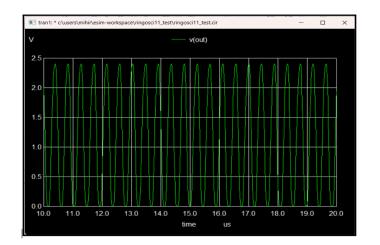

The design of conventional ring oscillator is made up of odd number of inverters connected in series that form a closed loop path. The stated design uses the similar concept in addition to power switching current starved inverters. The generation of high current is done by the symmetrical load, through which circuit becomes sensitive to very light variations in the input. The circuit is driven by proving the input Vin voltage set to 1 Volt pulse input, and reference voltage Vref is set to 1 Volt DC. MOS Transistor sizing is done with ratio of width to length as 240 nanometre to 130 nanometre respectively for nMOS and ratio of width to length as 600 nm to 130 nm respectively for pMOS in ideal conditions. The width of pMOS is double to overcome the drawbacks of pMOS and making pMOS work at almost the same speed as nMOS which in turn makes the resistance lower. If the input voltage is increased then the output of the circuit gets distorted. As the developed design circuit is used in applications which consume low power like biomedical appliances, chemical appliances, the lesser the provided voltage gives us the smoother output. With respect input, the output of the circuit is at the 0.06 percent of the input. For example, considering the input voltage as 1V, the oscillating output ranges between 0.7V to 1V. The output in real time simulation is not as same as the reference waveform, but is affected with high noise when there is transition from lower potential to higher potential.

Figure 4.46: Circuit diagram

Figure 4.47: Sub-circuit

Figure 4.48: Output waveforms

# 4.17 Miller compensated two stage operational amplifier

### 4.17.1 Circuit details

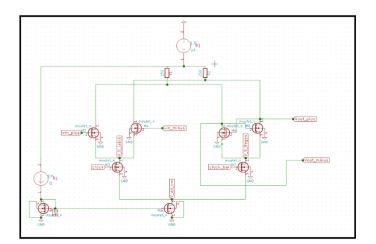

The circuit will have open loop gain of greater than 70dB phase margin greater than or equal to 60 degrees load capacitance of 10 pico farad and a minimum total power consumption. The load is assumed capacitive. compensation capacitor Cc can be treated open at low frequency. There are varieties of applications that opamp is applied on due to its linear device characteristic. In order to produce a good product differential inputs are applied to the amplifier to obtain a higher gain. The input differential amplifier block is designed to provide high input impedance large CMRR and PSRR low noise high gain and low offset voltage. The second stage of the opamp performs level shifting which added gain as well as the conversion of differential to single ended The circuit has a current mirror at the top differential pair in the middle and a tail current mirror. It also has a bias circuit at the left which is used to stabalize the transistor transconductance of opamp. The bias circuit supplies bias current to the circuit. Biasing circuit is independent of power supply voltage variations. The tail current mirror acts as a current source to the opamp. The input is given to the differential pair. The first stage of opamp is a differential pair with current mirrors and the second stage is a common source amplifier. The gain does not seem to be affected much to first order. The miller capacitance Cf is connected in negative feedback fashion across one of the internal gain stages typically the second stage.

Figure 4.49: Circuit diagram

Figure 4.50: Sub-circuit

Figure 4.51: Output waveforms

### 4.18 Current mode logic CML latch

### 4.18.1 Circuit details

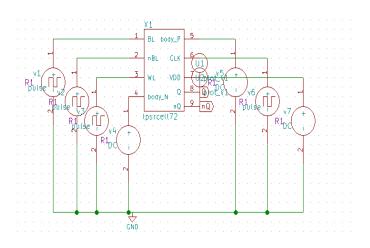

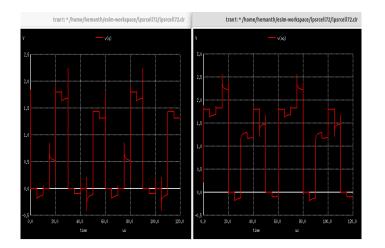

CML latch has the two sub parts: CML buffer and regenerative latch. The basic CML buffer is the simple differential amplifier with two resistor loads value R. Both transistor should be in saturation. The transistor which is closest to getting into triode is the one whose input is at VDD which can be treat as boundary condition. Hence, we must choose the logic swing Io into R to be less than threshold volatge of transistors. A regenerative latch in CML logic can be implemented by connecting the output to the input of CML buffer to get the positive feedback. For regeneration and latching, we need gm greater than 1/R. The input clocks of CML buffer and regenerative latch are complemented. To make sure all transistors are in saturation we must use appropriate common mode voltage. When clock is low, the second stage with positive feedback is disabled, and the circuit is a simple differential amplifier. This is the phase when the output tracks the input with some gain. When the clock goes high, the input amplifier stage is disabled, and the regenerative second stage is activated. The second stage then regenerates from where the amplification stage left the outputs and produces a logic output depending on the sign of the initial voltage. The designed circuit is only a latch. To make a flip flop that samples on every clock edge we need to use two latches in a master slave fashion.

Figure 4.52: Circuit diagram

Figure 4.53: Sub-circuit

Figure 4.54: Output waveforms

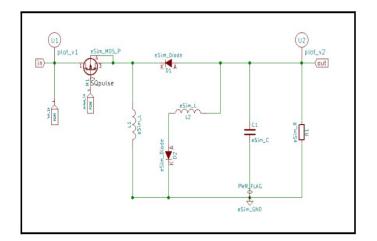

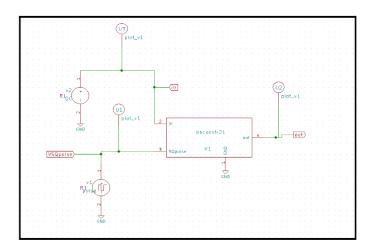

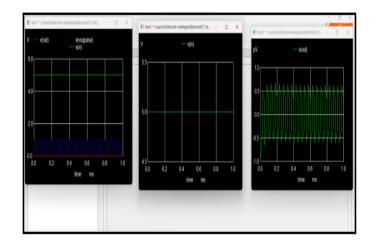

### 4.19 High Efficiency Dc-Dc Buck Boost Converter

### 4.19.1 Circuit details

The circuit is made by joining two converters, a buck converter, and a boost converter. Buck converter is a DC to DC power converter which steps down the voltage from its input to its output. Boost converter works exactly opposite to buck converter; it steps up the voltage from its input to its output. The circuit works on both principles of the buck converter and boost converter. The designed circuit is a combination buck and boost converter parallelly, therefore, we have to connect inductor L2 and diode D2 in the circuit. The proposed DC-DC buck-boost converter will produce negative output voltage with a low duty cycle and produce high voltage gain. The MOSFET present here worked as a high-frequency switch. Inductor L1 stores energy when the MOSFET switch is closed and supplies it to load and capacitor when the MOSFET switch is open. To store energy to transfer to output and filter it to get smooth voltage is the function of the capacitor. The proposed converter is arranged by 5V input DC source for superior efficiency, a MOSFET switch which is considered as a switching device where the switching has been set to 20KHz, as well as inductors L1 L2 set at 35mH, load resistance RL at  $50\Omega$  and output filter capacitor CL at  $1.1\mu$ F. The output voltage of the proposed DC-DC buck-boost converter is controlled by altering its MOSFET switch. DC-DC Buck-Boost converters can be developed by architecture improvement and by lowering parasitic resistance and capacitance.

Figure 4.55: Circuit diagram

Figure 4.56: Sub-circuit

Figure 4.57: Output waveforms

## 4.20 Gilbert Multiplier Cell

### 4.20.1 Circuit details

The Gilbert Multiplier Cell is an enhanced version of the source coupled cell and this allows four quadrant multiplication. Two cross coupled source coupled pair forms the structure of the circuit. It produces a particularly useful transfer characteristic. The circuit consists of mainly 4 transistors namely M1, M2, M3, M4. The DC transfer characteristics of the multiplier circuit are the product of the hyperbolic tangent of the two input voltages. The multiplier cell always remains in the saturation region during normal operation. Used in this way the circuit is capable of performing precise multiplication of one continuously varying analog signal by another, the input signal is given at the source terminal junction of the two source coupled cells and the output is taken at the drain terminal of each source coupled cells. Furthermore, the collected output from the drain terminal is passed to a series of three inductor capacitor networks thereby preventing the loading effect at the output terminal of the device. The circuit can operate at lower supply voltages and better noise performance due to the low parasitic ohmic resistance of the inductors. The lower common-source transistors are fed by the differential mm Wave LO signals and the upper quad is composed of thick oxide transistors ensuring reliability against high swings at the drain nodes.

Figure 4.58: Circuit diagram

Figure 4.59: Sub-circuit

Figure 4.60: Output waveforms

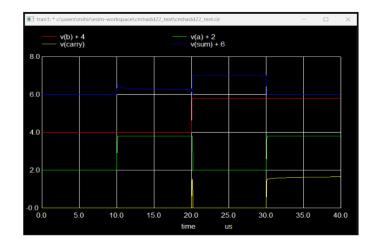

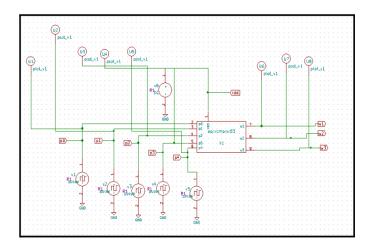

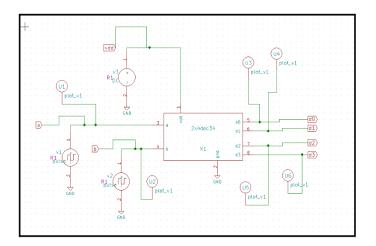

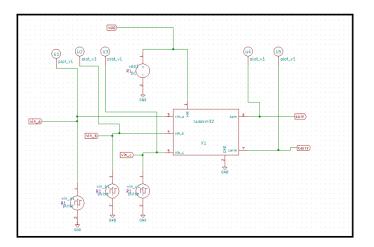

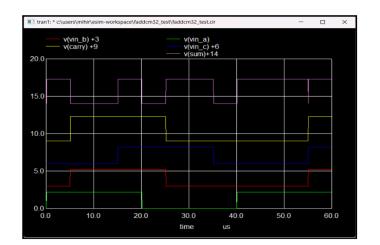

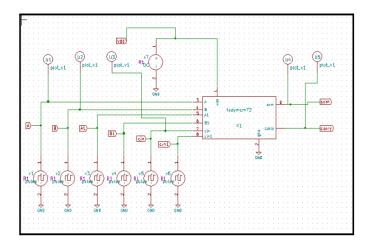

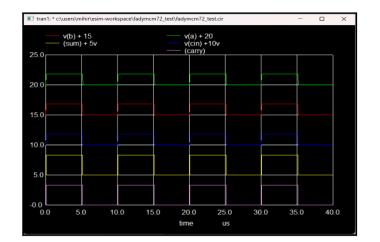

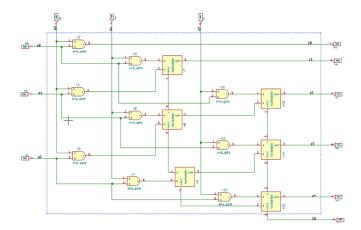

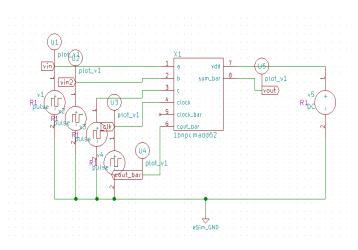

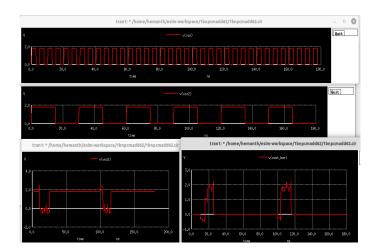

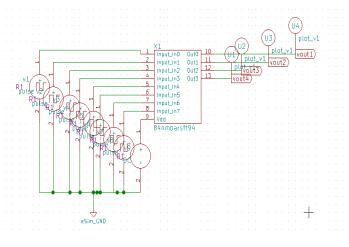

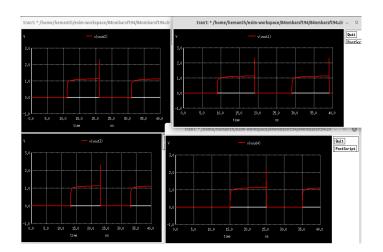

## 4.21 32-bit ALU

### 4.21.1 Circuit details

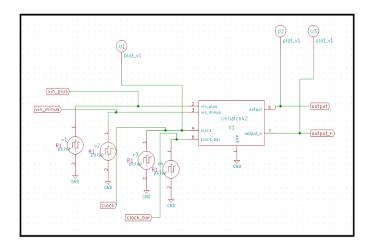

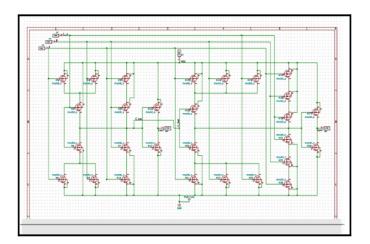

The proposed ALU is capable of 4 operations- addition, subtraction, logical AND, logical OR on 32 bit numbers. here, I have implemented addition & subtraction & with addition of logical AND which is already part of Full adder logical OR, this block can be called as 1 bit ALU such 32 blocks are cascaded to form 32 bit ALU of which operation can be controlled by 4:1 MUX. Talking about 32-bit ALU which i studied for this project (reference website in readme file) 32-bit ALU which takes two 32-bit values is capable of 4 operations – addition, subtraction, bitwise AND, bitwise OR which is selected by 2 control lines generate one 32-bit output. Along with that, it also has 3 status outputs – zero, carry, overflow. A typical 32-bit ALU is rather much more complex than this but its simplified version of ALU which can be easily implemented using basic logic gates. The 4 logic gates which are used in this are AND, OR, NOT XOR. Along with that to choose between various operations to perform, multiplier is used which is controlled by control signal connected to its select lines. VLSI runs on 3 main factors – Area, Power & Performance, & therefore, to use area in efficient manner, we are going to use inversion for one of the inputs while performing subtraction which in result allow us to use same adder circuitry for subtraction purpose too.

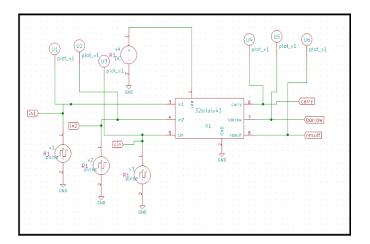

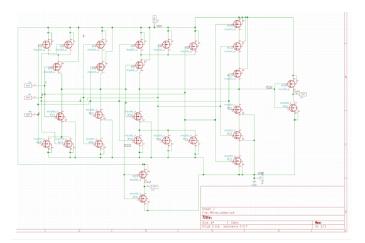

Figure 4.61: Circuit diagram

Figure 4.62: Sub-circuit

Figure 4.63: Output waveforms

## 4.22 Full Adder using CMOS

### 4.22.1 Circuit details

The full adder circuit has 3 inputs – A, B and Cin. It has 2 outputs – Sum and Cout, and thus there are 2 sets of pull-up and pull-down networks. As we know, the pull-up network consists of pMOS and the pull-down network consists of nMOS transistors. In the circuit for the Carry output, there are 5 of both pMOS and nMOS transistors. Now, we know that the equation for the Sum output is conventionally given by (A exor B exor C). But, this gives rise to complications in designing the circuit as there would be a lot of transistors, and the circuit would be very expansive. Thus, we go for an alternative path and take the Cout bar output and feed it into the Sum circuit as the 3rd input. This eases the equation for the Sum output by expressing it in terms of A, B, Cin and Cout, rather than exor operations. It also reduces the number of CMOS transistors required in the Sum circuit and hence the overall design. We obtain the required number of both pMOS and nMOS as 7 for the Sum. Also, since CMOS circuits always provide an inverted output, we need to add inverter circuits to both the Sum and Cout outputs to acquire the originally required outputs - hence costing us 2 more of both pMOS and nMOS for each output inverter. The number of CMOS transistors used thus comes to a total of 28. NOTE : The waveform obtained although correct and in accordance with the truth table of Full Adder, does not exactly resemble the reference waveform provided in the literature survey report.

Figure 4.64: Circuit diagram

Figure 4.65: Sub-circuit

Figure 4.66: Output waveforms

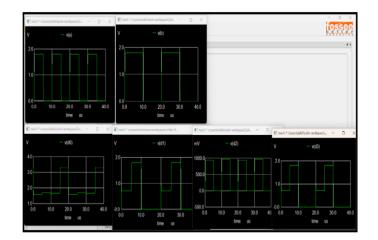

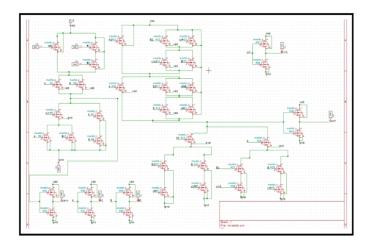

## 4.23 Full Adder implementation on Dynamic CMOS Logic

#### 4.23.1 Circuit details

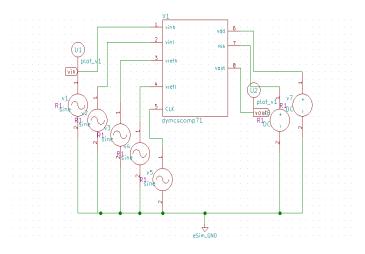

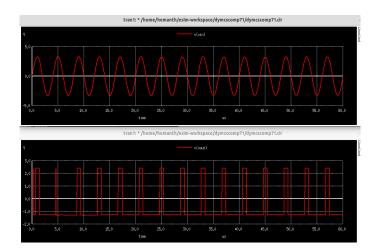

The circuit is implemented using the using CMOS logic (combination of MOS-FETS(i.e.NMOS and PMOS)). The Full adder circuit Has two output (i.e. Sum output and Carry ouput). At first, The circuit. Equations are reduced for implementing the circuitry. The circuit totally consists of 40 mosfets considering both Sum and carry circuit. As CMOS logic gives an inverted output an Inverter is used For realising the Actual output. The inputs to the circuit Are A, B, cin. A1, B1, cin1. Here A1, B1 and cin1 are the inverted values of input A, B and cin respectively Which are used While realising The Ouput of Sum Circuit. The equation realised for obtaining Sum output is A1(B1cin+Bcin1) + A(B1cin1+Bcin). Similarly the equation realised for obtaining Carry output is cin(A+B)+AB. The Complete circuit simulation is done Through esim simulator Where Annotations check, Electrically rule check and Netlist generation Tasks are proceeded. The Output of Simulation(Netlist) is mapped with Librabries of Skywater 130nm PDK. Here Skywater 130nm technology is a mature 180nm-130nm hybrid technology Developed by Cypress semiconductors and Later Collabarated with Google which is open sourced for industry usage. The Output Waveforms for the Designed circuitry with Generated Netlist Mapped with SKY130 nm Libraries are checked using Ngspice (Which is also a open Source Spice simulator Tool). Thus the output waveform is Then checked for correctness and functionality For the implementation of Full adder circuit.

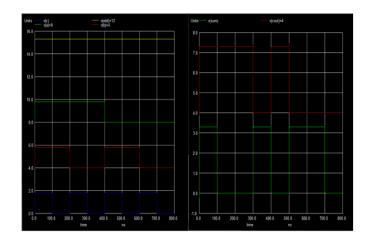

Figure 4.67: Circuit diagram

Figure 4.68: Sub-circuit

Figure 4.69: Output waveforms

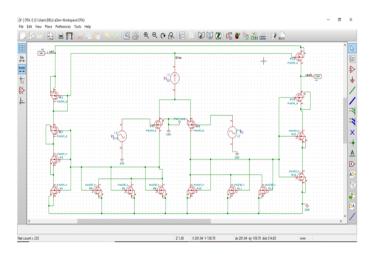

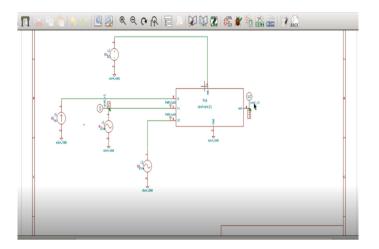

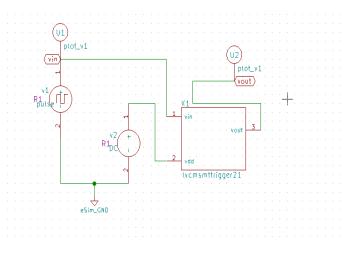

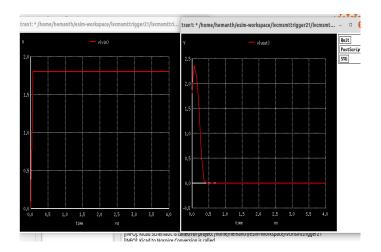

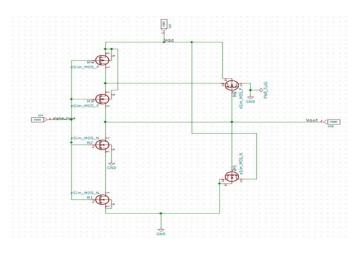

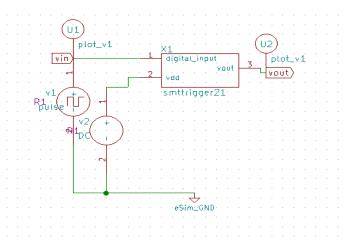

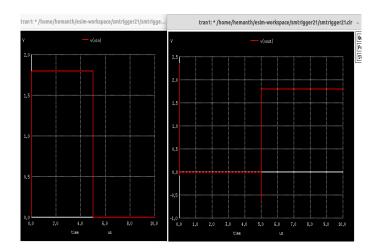

## 4.24 CMOS SCHMITT TRIGGER

### 4.24.1 Circuit details

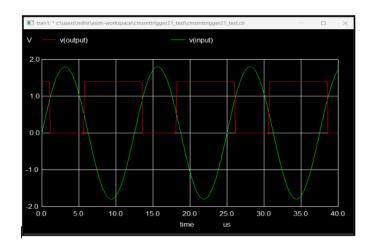

The input of the Schmitt trigger is tied to the gates of four CMOS devices. The upper two are PMOS and the lower two are NMOS. Transistors M6 and M3 act as source followers and introduce hysteresis by feeding back the output voltage. The Schmitt trigger circuit can be divided into two parts depending on whether the output is high or low. When the output is low and the input is high the transistors M5 and M4 are OFF and M6 is ON. As M6 is ON it creates an additional path to the ground for node X. When Vin makes the transition from Vdd to 0, transistors M5 and M6 will turn ON. But some current charging output will be diverted through this node X to the ground until the output goes high and turns OFF M6.So Vin has to go much lower for the transition. Similarly, When the output is high and the input is low the transistors M1 and M2 are OFF and M3 is ON. So when M3 is ON there will be a path to the Vdd for the node Y. When Vin makes the transition from 0 to Vdd, transistors M1 and M2 will turn ON and will try to pull the Vout to the ground but before that, it has to sink the additional current from Vdd, until the output goes low and turns OFF M3. Hence, Vin has to go much higher to make the output low. The upper and lower threshold voltages of the Schmitt trigger are set by choosing appropriate W and L of PMOS NMOS transistors.

Figure 4.70: Circuit diagram

Figure 4.71: Sub-circuit

Figure 4.72: Output waveforms

## Chapter 5

## IPs done by Ayush Kashyap

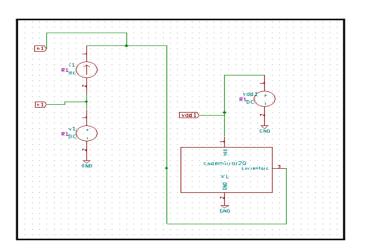

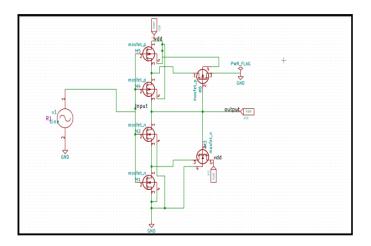

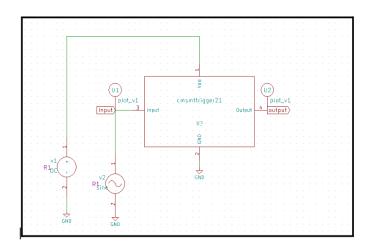

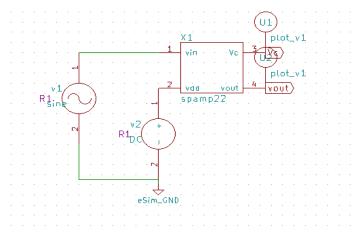

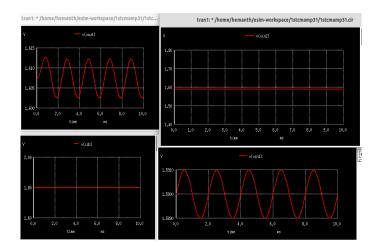

## 5.1 Ideal Circuit:Design of low transconductance OTA

### 5.1.1 Circuit details

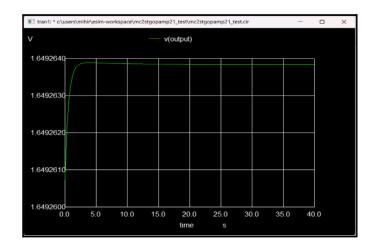

Operational Amplifiers Opamps were widely used in many analog circuit implementations. But due to power hungry and frequency limit characteristics Opamps has been replaced by Operational Transconductance Amplifier OTA.OTA is widely used for the conversion of voltage to current. In OTA differential input voltage produces current as output and it is a voltage controlled current sources VCCS.Low transconductance transconductor and low power is required for biomedical applications. Transconductance has importance in CMOS analog circuits it indicates the ability of device to transfer input voltage to output current. The PMOS current mirrors are placed in series and parallel to achieve the Transconductance. An ideal Operational Transconductance Amplifier OTA has two input voltages with infinite input impedance. The voltages Vin- as v1 and Vin+ as v2 are the inverting and non-inverting input voltages applied to the circuit. The current Ibias is the bias current which mainly helps in controlling the gain of the amplifier. The bias current Ibias is proportional to the transconductance of Operational Transconductance Amplifier OTA. The transconductance can be calculated by using series parallel as Gm is equal to gm1/N2 where transconductance of the transistor M7 is gm1 and Number of transistors in series and parallel is N. series parallel current division was applied in symmetrical OTA to achieve low transconductance with extended linear region.

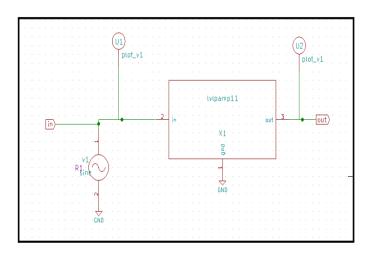

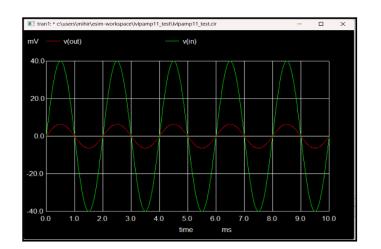

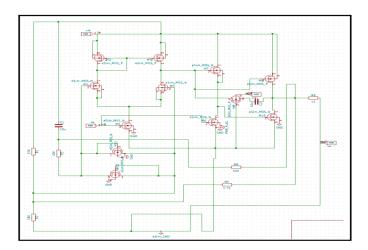

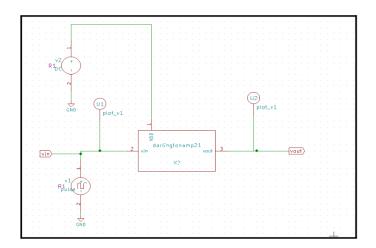

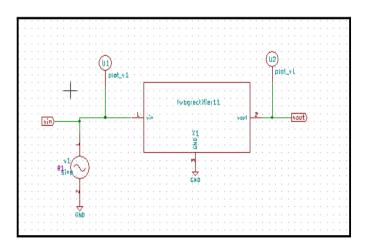

Figure 5.1: Circuit diagram

Figure 5.2: Sub-circuit

Figure 5.3: Output waveforms

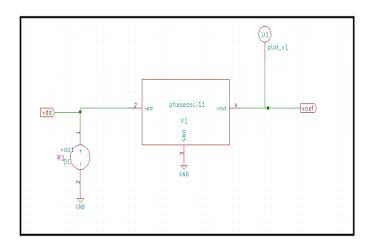

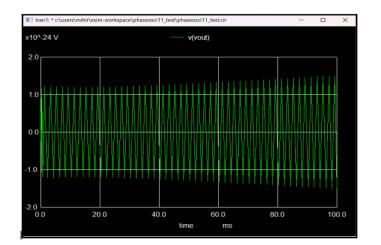

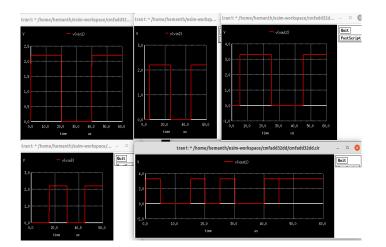

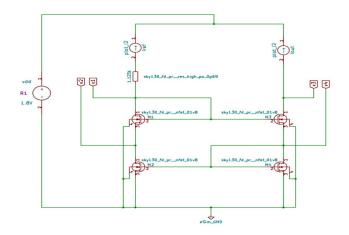

## 5.2 RING OSCILLATOR

### 5.2.1 Circuit details

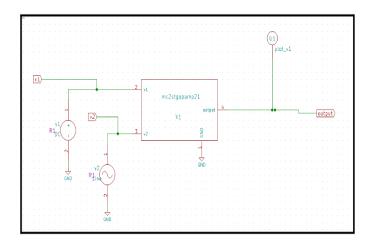

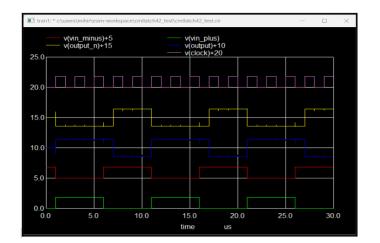

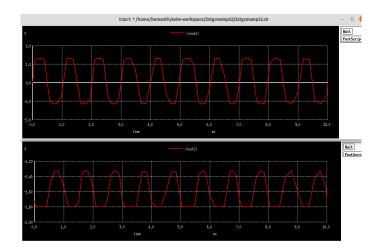

Odd number of stages gives the inverted output when the input voltage is given at once to the first stage, the oscillation starts. When oscillation begins, Barkhausen Criteria must be satisfied to sustain stable oscillation. Ring Oscillators are composed of a number of inverters or delay stages connected to each other in the form of a chain, with the output of the last stage fed back to the input of the first The most important factor in ring oscillator is gate delay because in devices fabricated with MOSFET, gate cannot switch immediately. The gate capacitance needs to be charged before current flows between drain and source so that every inverter takes time to give output. Therefore increase in the number of stages of ring oscillator increase the gate delay. Odd number of inverter stages used to give the effect of single inverter amplifier with a negative feedback gain of greater than one so that the output will be in opposite direction to the input and it will be amplified with an amount more than the input. Amplified, inverted output is then propagated to the input with delay where it is amplified and inverted again. Digital and analog circuits have an important factor known as the propagation delay or gate delay. Propagation delay in ring oscillator is defined as the time difference between input and output. And the applications are Ring oscillators can also be used to measure the effects of voltage and temperature on a chip. The voltage-controlled oscillator in most phase-locked loops is built from a ring oscillator.

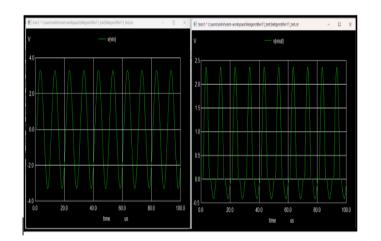

Figure 5.4: Circuit diagram

Figure 5.5: Output waveforms

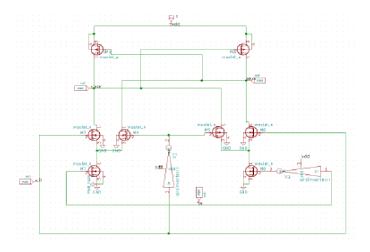

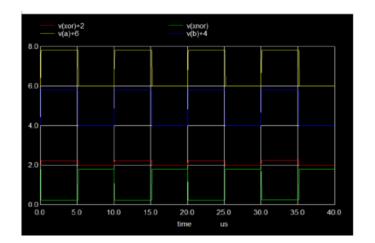

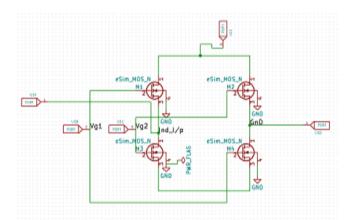

## 5.3 CMOS Differential cascade voltage switch logic(DCVSL) XOR-XNOR

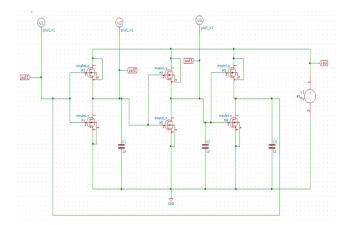

### 5.3.1 Circuit details

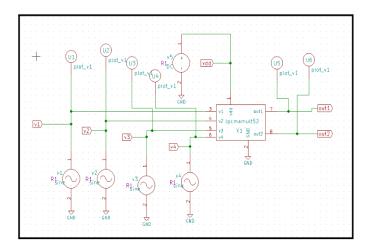

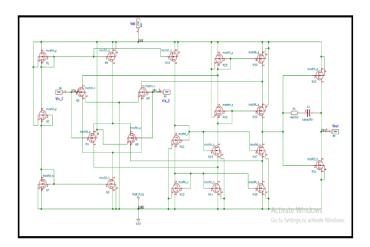

When the differential pairs of MOSFET devices are cascaded into strong combinational logical tree networks, then we can achieve a design leverage in CVSL which is within a single circuit delay and is capable of implementing complex Boolean logic. A DCVS Logic is based on 2 to 1 Multiplexer which is used as an important element in many various circuit designs such as implementation of memory circuits and FPGA. A differential gate requires that each input is provided in a complementary format, and it produces complementary output in return. The feedback mechanism ensures that the load is turned off when it is not needed gives rise to the DCVSL family in CMOS circuits. The circuit uses 2 static PMOS in the pull up network. The pull down networks PDN1 and PDN2 are built using NMOS and are mutually exclusive. The PDN networks are connected as the inputs to the PMOS in a crossed manner. In general, the PMOS devices are deemed to be active low devices i.e conducts when given low voltage and NMOS being active high devices i.e conducts when given high voltage. The low GND and high VDD voltages that are supplied are mapped to the binary 0 and 1. When inputs are given to the a and b terminals, the actual and complementary values are taken. There is only one PDN active at the same time considering the logic. The PDN that is not active is isolated from the VDD and the ground. This circuit can further be used in adder and multiplier circuits. The outputs of the xor and xnor gates are obtained simultaneously

Figure 5.6: Circuit diagram

Figure 5.7: Sub-circuit

## 5.4 Low Noise Low Power Amplifier for Biomedical Applications

### 5.4.1 Circuit details

CMOS technologies paved way to increasing market of mobile and portable electronic devices. This growth is driven by the continual integration of complex analog and digital building blocks on a single chip. The operational transconductance amplifier is an important analog building block and for many applications is the largest and most power consuming. Recently, one of the most commonly used architectures whether as a single-stage or first stage in multistage amplifiers had been the folded cascode amplifier for its high gain and reasonably large signal swing in the present and future low voltage CMOS processes. Biomedical signals have weak amplitude and low frequency so we need to amplify these signals. Amplifiers should have basic features like high CMRR low power consumption low input referred noise for good performance in the field of biomedical engineering. There are many ways to design the amplifier with above conditions. For example implementation here is two stage gate driven folded cascode amplifier. In addition to reduce the flicker noise PMOS input transistors with large gate areas are used for low power operation. Ib current in M0 Mc1 and Mc3 is mirrored by Mb then M0 supplies the first stage current. M13 and M14 currents are controlled by Mc1 and Mc2. Equal drain potentials is maintained by M13 and M14 across the Ma3 Mb3 and Ma4 Mb4 in order to improve matching. Cc and Rc are used between the drain of M8 and output terminal for compensation, So it improves the phase margin and GBW

Figure 5.8: Circuit diagram

Figure 5.9: Sub-circuit

## 5.5 ONE BIT MIRROR ADDER

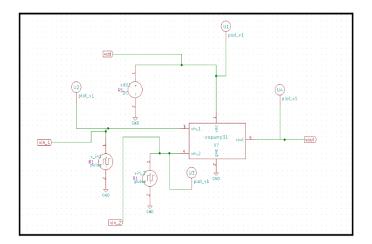

#### 5.5.1 Circuit details

One bit Mirror adder adds up three binary inputs – A, B, Cin and produce 2 binary outputs – Sum and Carry out. Mirror adder does not have complementary pull-up and pull-down circuit. Instead, it has symmetric mirroring circuit. Which means, the same circuitry is found for both NMOS logic and PMOS logic. The circuit that needs to be implement a onebit mirror adder is shown in Fig1. The design implemented gives us Sum and Cout and the equations are obtained from normal one-bit full adder sum and carry out equations. If you see 1-Bit mirror adder you might not see much difference in processing time but if you construct multi-bit mirror adder, the advantages mentioned below can be observed especially in Carry ripple adder. Advantages: 1. In carry ripple operation, the critical path is from Cin propagated till Cout so Carry will be computed fast in mirror adder which will help in fast up the multi bit carry ripple adder. 2. A smaller number of transistors were used to implement logic i.e., 28 transistors. 3. We do not need inverted inputs. 4. It will have a uniform layout. For simulating the spice generated from the eSim, ngSpice is used. The inputs in the spice were added in such a way that 8 combinations of the inputs can be verified. To get the proper output I have same width and length ratio for all NMOS and PMOS.

Figure 5.10: Circuit diagram

Figure 5.11: Sub-circuit

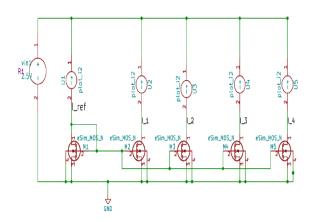

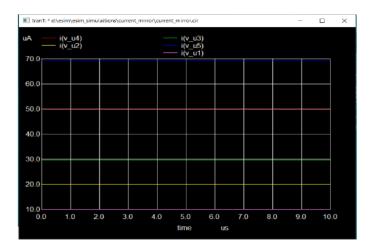

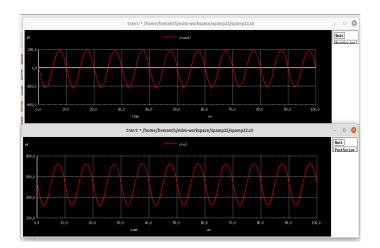

## 5.6 MIRROR WITH MULTIPLE OUTPUTS

### 5.6.1 Circuit details

The current mirror circuits are simple current sources which gives constant current In other words we can define it as a A two terminal circuit whose output current is independent of the output terminal voltage and depends only on the input current Generally it is used to generate a replica of given reference current The current mirror circuits are based on the principle if the gate to source voltage of two identical MOSFETs are equal then the drain current flowing through them is equal A current mirror can be thought as a current controlled current source Ideally the output impedance of a current source should be infinite and capable of generating or drawing a constant current over a wide range of voltages A current flows through M1 corresponding to VGS1 Since VGS of all the MOSFETS are shorted ideally the same current has to flow through the all other MOSFETS but by adjusting the W to L ratio we can get a different current as per our requirement a multiple of the current in M1 or the fraction of the current flows through M2 M3 M4 M5 If the MOSFETs are of the same size the same drain current flows in each MOSFET provided M2 M3 M4 M5 stays in the saturation region The circuit diagram for the basic current mirror with multiple output currents has been uploaded in the reference circuit file this circuit is obtained by extending the basic current mirror to give multiple outputs here i have used all n type MOSFETS

Figure 5.12: Circuit diagram

## Chapter 6

## IPs done by Narra Hemanth

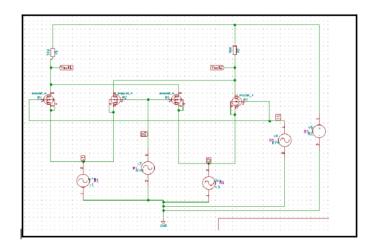

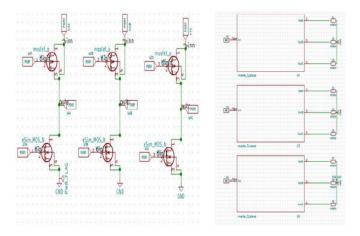

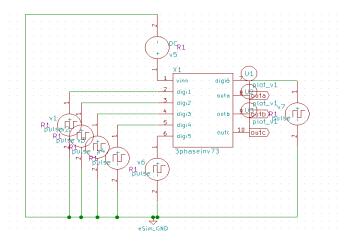

### 6.1 THREE PHASE INVERTER

#### 6.1.1 Circuit details

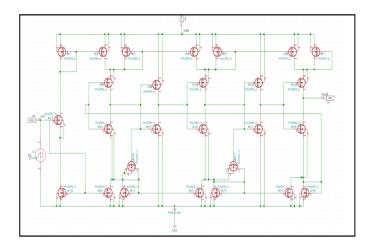

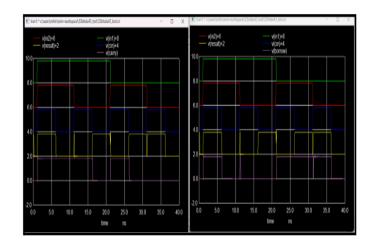

The schematic diagram considered here is a nine-phase voltage source inverter where a DC supply is converted to a nine-phase AC supply. There are three, three-phase inverter sub circuits in the circuit shown in figure.1. Each sub circuit consists of six electronic switches as shown in the sub circuit figure .2, Switches in the same limb should not conduct simultaneously as it leads to a short circuit of the supply. The excitation sequence is S1, S6, S3, S2, S5, and S4. Each switch conducts for 180 degrees and delays by a phase angle of 60 degrees as mentioned in the previous sequence. The output from this inverter is fed to a 3-phase balanced load. The output voltage is 120 degrees out of phase. As a three sub circuit works combined to get the nine-phase voltage. The simulated circuit does not use any anti-parallel freewheeling diode connected across each electronic switch. In this case, the output drove only for R load, if we use L C load then we should use an anti-parallel freewheeling diode to protect switches from discharging current. The combined Waveform of loads A, B, and C are shown in the figure. waveform.1. The other three wave forms show quasi-square wave forms between each combined load of A and B, similarly, B and C, C and A, as shown in the figure. Waveform.2, Waveform.3, Waveform.4. The input Dc voltage is 25v given to the inverter and the output drawn from the inverter is 40v Ac Here the schematic diagram is drawn using esim and simulated by ngspice.

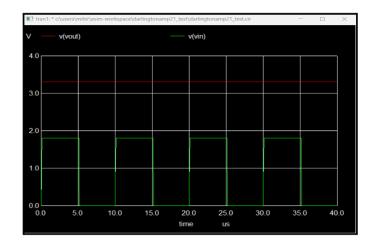

Figure 6.1: Circuit diagram

Figure 6.2: Sub-circuit

Figure 6.3: Output waveforms

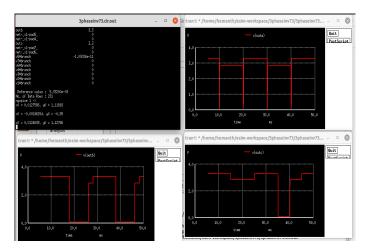

# 6.2 Low power and High speed 1 bit full adder circuit

#### 6.2.1 Circuit details

Many applications like DSP architectures which are application specific and microprocessors have been widely used in many VLSI Systems. In most of these systems, the adder is a component of the Critique, which defines the systems overall performance. As a result, enhancing the performance of the one bit adder cell is a critical objective as Due to the rapid rise of technologies in mobile communication and computing, the construction of low-power VLSI systems has recently acquired traction. Battery technology, on the other hands not growing as quickly as microelectronics technology. However, the amount of energy available to mobile systems is restricted . As a result, designers are faced with increased constraints, such as high speed, high performance, tiny silicon area, and low power consumption. So, in today's VLSI world, developing a low-power, high performance adder cell is essential. This adder is made up of ten CMOS transistors with a 4T XOR logics. This design is known as a low-power adder since it does not have a direct link to the ground and can re-apply the load charge to the control gate, which is why it is also known as a Static energy recovery complete adder. The design technique takes three inputs and produces two sum and carry outputs. The low power consumption of this circuit is a benefitted in small area and less PDP compare to pass transistor logic (PTL).

Figure 6.4: Circuit diagram

Figure 6.5: Sub-circuit

Figure 6.6: Output waveforms

## 6.3 Sziklai Pair Amplifier

### 6.3.1 Circuit details

This project focuses on design of a Sziklai Pair Amplifier using Google Skywater (sky130) Technology node with operating voltage of 1.8V and 3.3V. The project is build using Open Source Tools like Magic, Sky130PDK and eSim. Refer following website for more details on Sziklai Amplifier: https://en.wikipedia.org/wiki/Sziklai pair.

Figure 6.7: Circuit diagram

Figure 6.8: Sub-circuit

Figure 6.9: Output waveforms

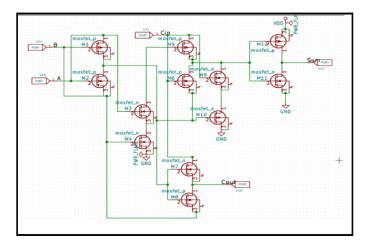

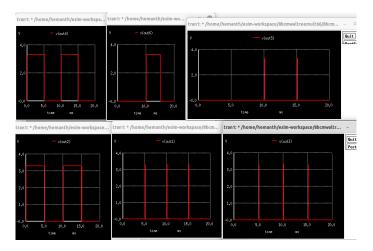

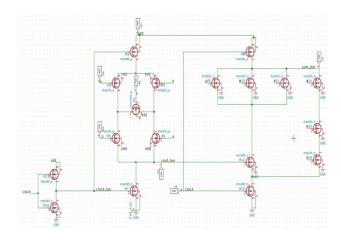

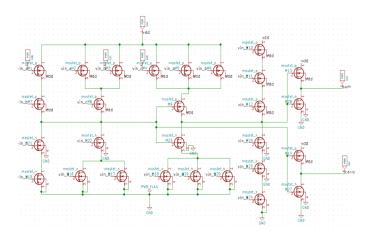

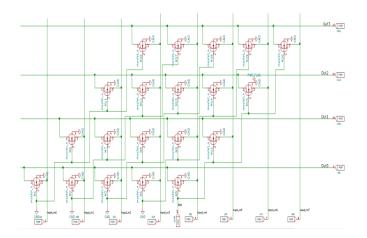

## 6.4 Implementation of a 3-bit CMOS Wallace Tree Multiplier

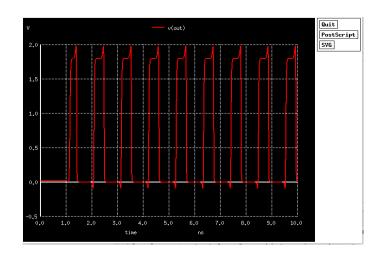

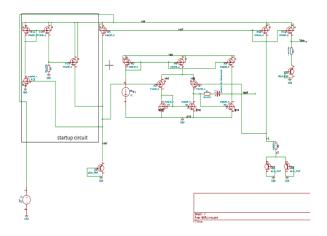

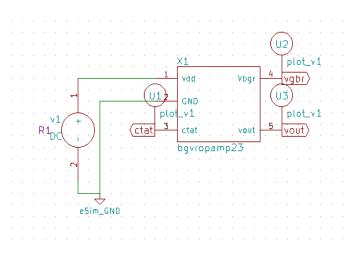

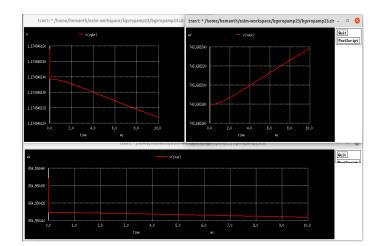

### 6.4.1 Circuit details